用动图的方式,理解 CPU 缓存一致性协议!

我先给大家复习下 MESI 协议,然后再跟大家讲一些这个网站怎么用。

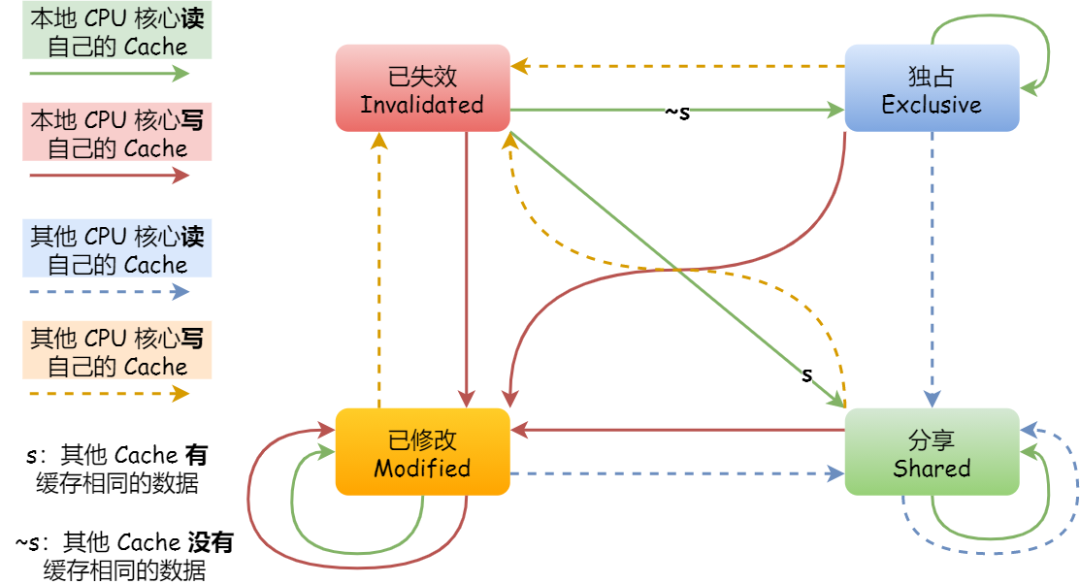

MESI 协议

Modified,已修改

Exclusive,独占

Shared,共享

Invalidated,已失效

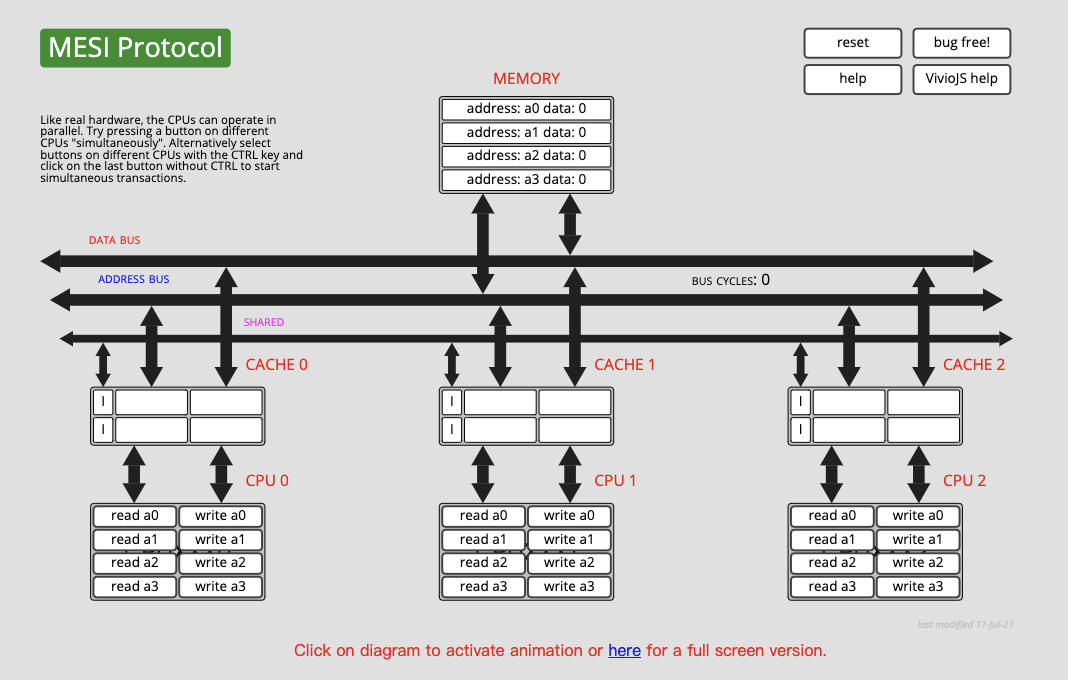

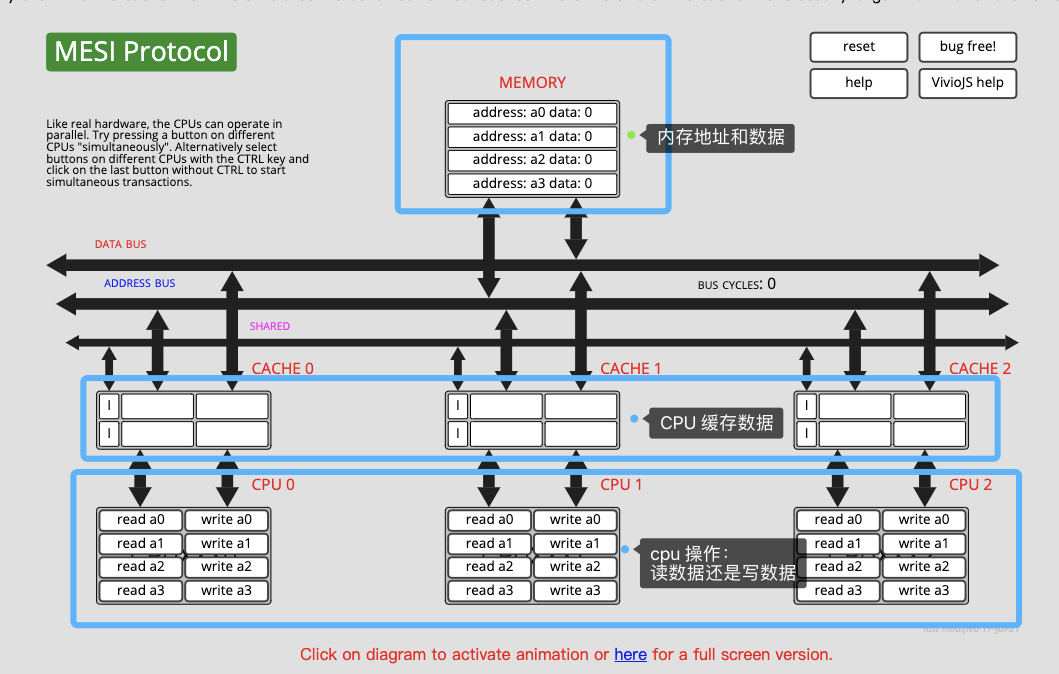

网站体验

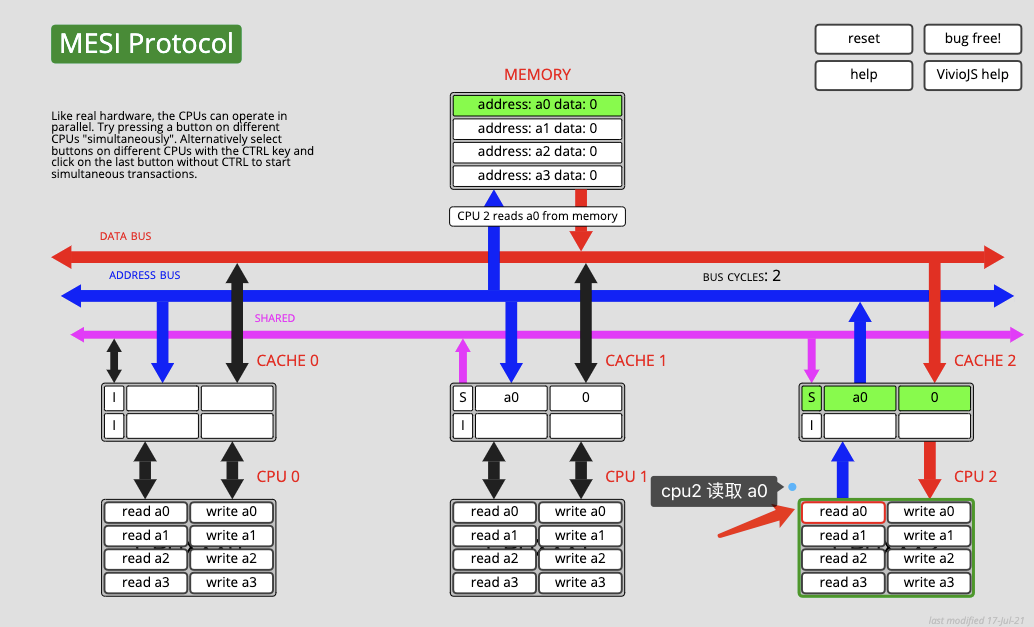

第一部分,内存。显示内存地址和数据;

第二部分,CPU 缓存。显示 CPU 缓存的变量数据和 MESI 协议状态,因为我现在还没开始操作,所以显示的是空白。

第三部分,CPU 操作。共有三个 CPU,每个 CPU 都有各自的 Cache,CPU 操作分别「读」和「写」,这部分是我们手动操作的部分。

数据总线(Data Bus):在CPU与内存之间来回传送需要处理或是需要储存的数据。

地址总线(Adress Bus),用来指定在内存之中储存的数据的地址。

shared,这个我也不知道是什么总线,网上没搜到资料,网站上最细那条总线就是这个名字,作用是控制 Cache 的数据状态。

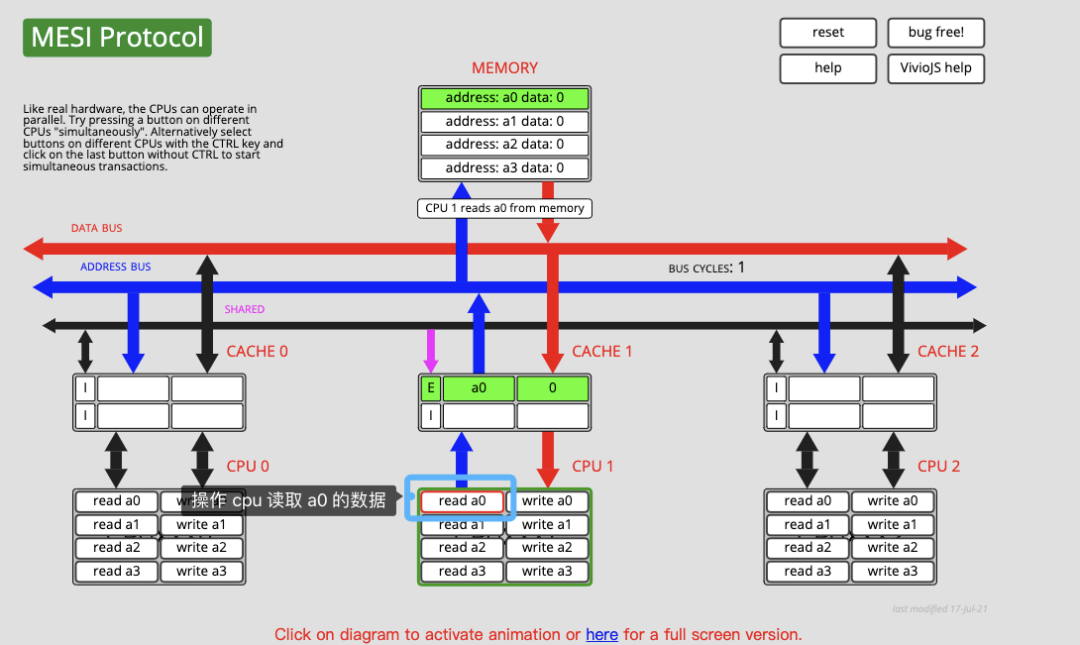

点击 CPU2 的 read a0 操作;

CPU2 会向地址总线,发送读取 a0 变量的数据的请求,此时该请求不仅会被内存收到,也会被其他 CPU 核心收到。

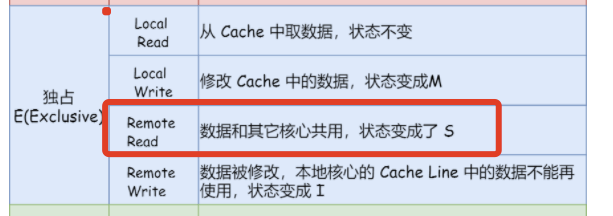

CPU1 从地址总线得知,CPU2 发起的读取地址存在于 CPU1 Cache 里,于是 CPU1 Cache 里数据的状态会从 E(独占)变更为 S(共享);

内存收到 CPU2 发起的读取 a0 数据的请求后,就会通过数据总线将数据传递给 CPU2;

最后数据会写到 CPU2 Cache 里,且状态是 S(共享)。

评论