印度将发力RISC-V处理器

共 2294字,需浏览 5分钟

·

2022-02-16 08:35

RISC-V 架构的主要优势之一是它是开放的,因此任何具有适当技能的组织都可以开发自己的内核,印度政府利用微处理器开发计划 (MDP) 帮助开发 VEGA RISC- 抓住了这个机会本地 V 核。

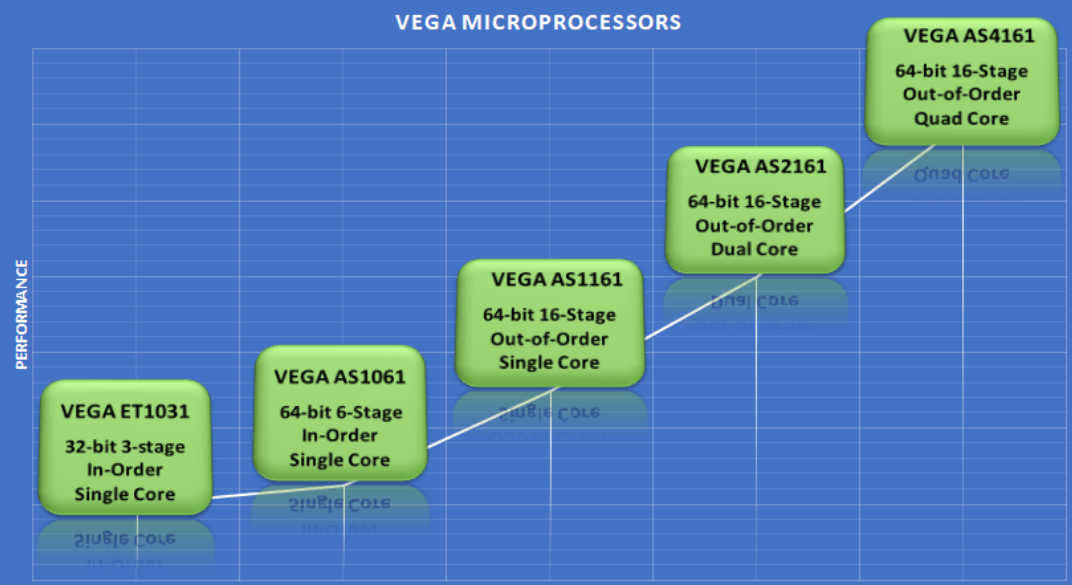

在电子和信息技术部 (MeitY) 的资助下,先进计算发展中心 (C-DAC) 成功设计了五个 RISC-V 处理器,从单核 32 位 RISC-V 微控制器级处理器到支持 Linux 的四核 64 位乱序处理器。

C-DAC 开发的五个 VEGA 内核的主要特性:

VEGA ET1031 – 32 位单核 3 级有序 RV32IM 处理器,带AHB/AXI4.bus,可选 MMU,可选调试

VEGA AS1061 – 64 位单核 6 级有序 RV64IMAFDC 处理器,具有 8KB D-cache、8KB I-cache、FPU、AHB/AXI4总线

VEGA AS1161 – 64 位单核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、FPU、AHB/AXI4/ACE总线

VEGA AS2161 – 64 位双核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、512KB L2 cache、FPU、AHB/AXI4/ACE 总线

VEGA AS4161 – 64 位四核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、1024KB L2 高速缓存、FPU、AHB/AXI4/ACE 总线

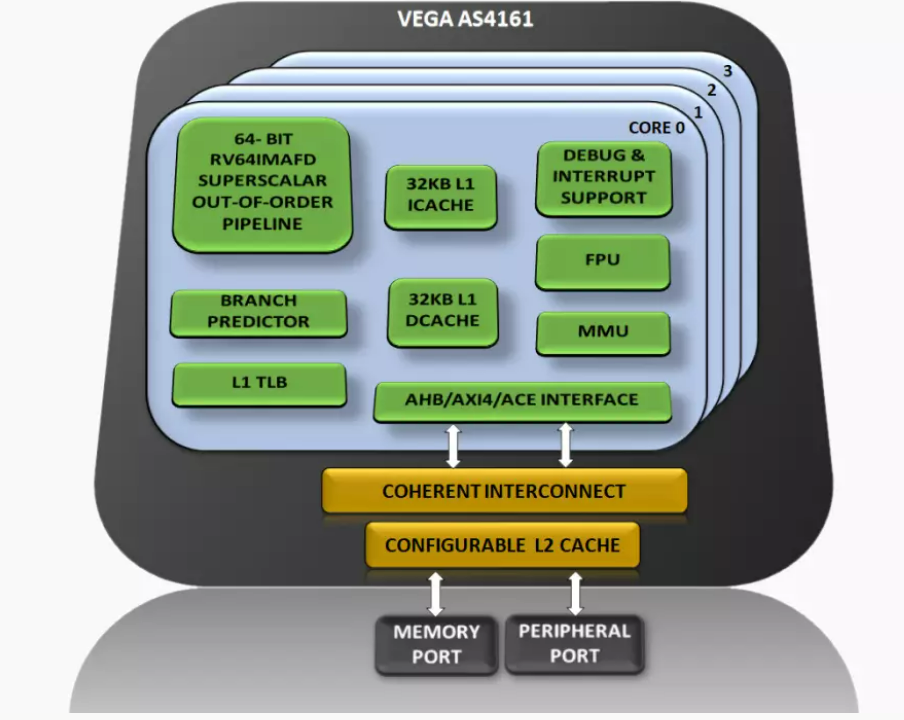

深入了解高端 VEGA AS4161 的主要特性:

· RISC-V 64G (RV64IMAFD) 指令集架构

· 13-16阶段乱序流水线实现

· 高级分支预测器:BTB、BHT、RAS

· 哈佛架构,独立的指令和数据存储器

· 用户、主管和机器模式权限级别

· 支持 Linux 的全功能内存子系统

内存管理单元

基于页面的虚拟内存

可配置的 L1 缓存

可配置的二级缓存

· 高性能多核互连

· 符合 IEEE 754-2008 的高性能浮点单元

· AXI4- / ACE,兼容外部接口

· 平台级中断控制器

多达 127 个 IRQ

低中断延迟

· 向量中断支持

· 高级集成调试控制器

JTAG 兼容接口

硬件/软件断点支持

· 调试扩展允许通过 GDB >>openOCD >> JTAG 连接进行 Eclipse 调试

· 兼容 Linux

预计不会很快就会有桌面 Linux 的处理器,因为 AS4161 主要针对存储和网络应用程序。

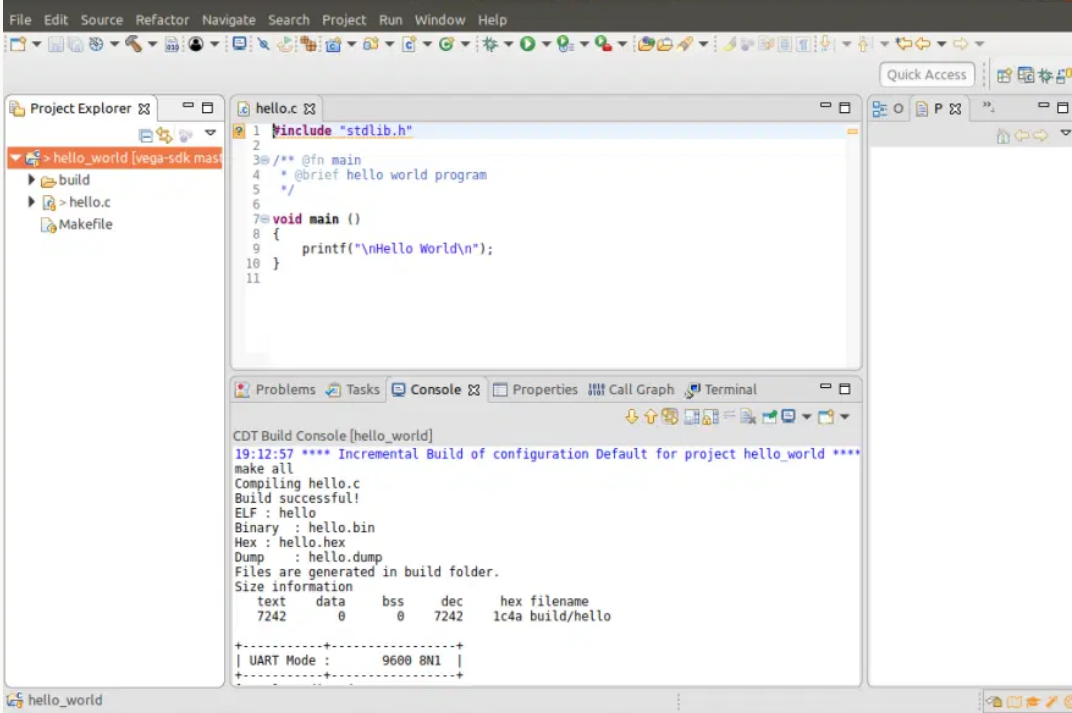

更好的是两个 SoC(THEJAS32和 THEJAS64)的文档的公开可用性,分别基于 VEGA ET1031 和 VEGA AS1061 内核,HDL代码在ARTYA7 FPGA 板上运行(A7-35T可以运行 THEJAS32,但 A7-100TTHEJAS64 需要)。带有 Eclipse IDE的C/C++ VEGASDK允许工程师为该平台开发程序,并且还提供了用于 64 位 VEGA 处理器的Linux 源代码。代码托管在 Gitlab 上,但您需要在检索代码之前请求访问...这有点令人失望。

印度政府还计划为 VEGA 处理器举办培训课程,但该页面目前是空的。找不到任何有关 VEGA 的时间表以及制造是否会在印度进行计划的信息。该项目的博客已经好几个月没有更新了,但“VEGA处理器”的YouTube账号在2022年1月31日上传了一段视频,对五款VEGA RISC-V处理器进行了概述(来源:cnx-software)。

项目网站(https://vegaprocessors.in/)。

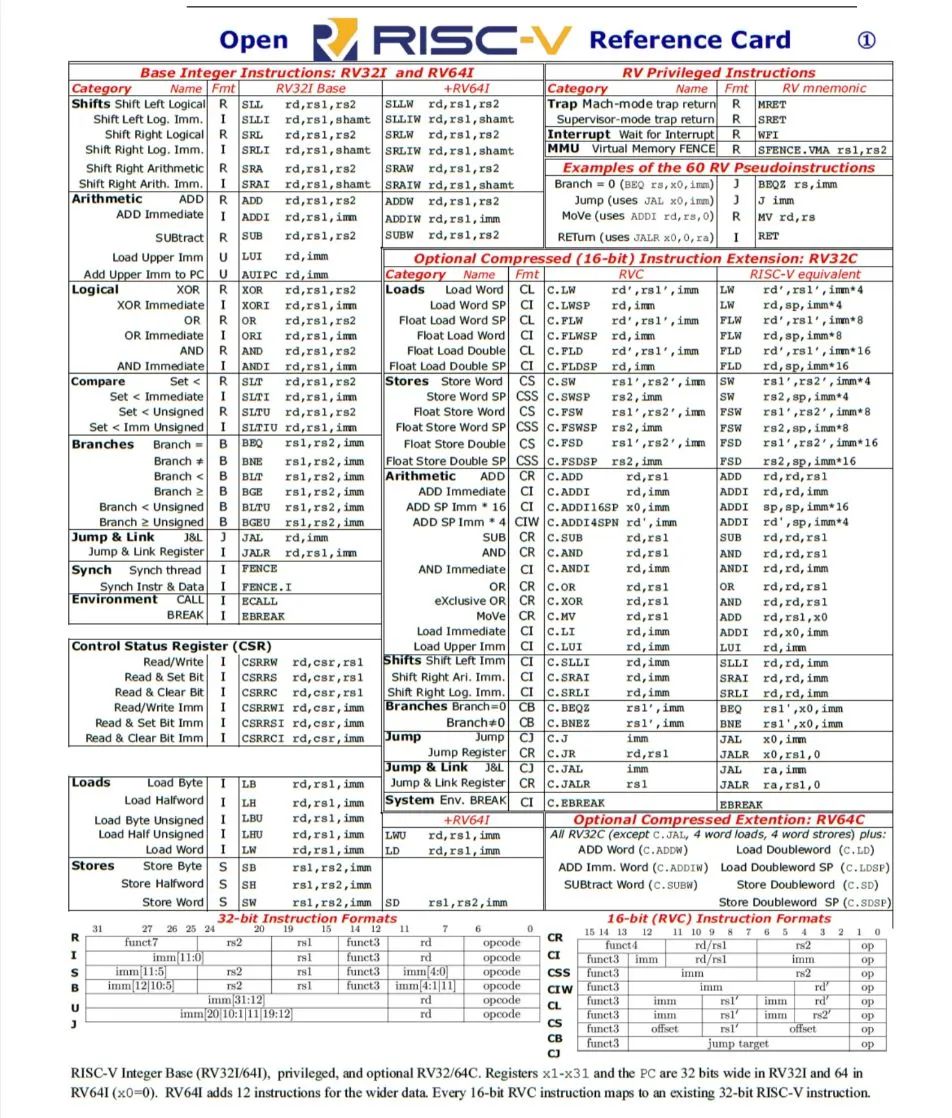

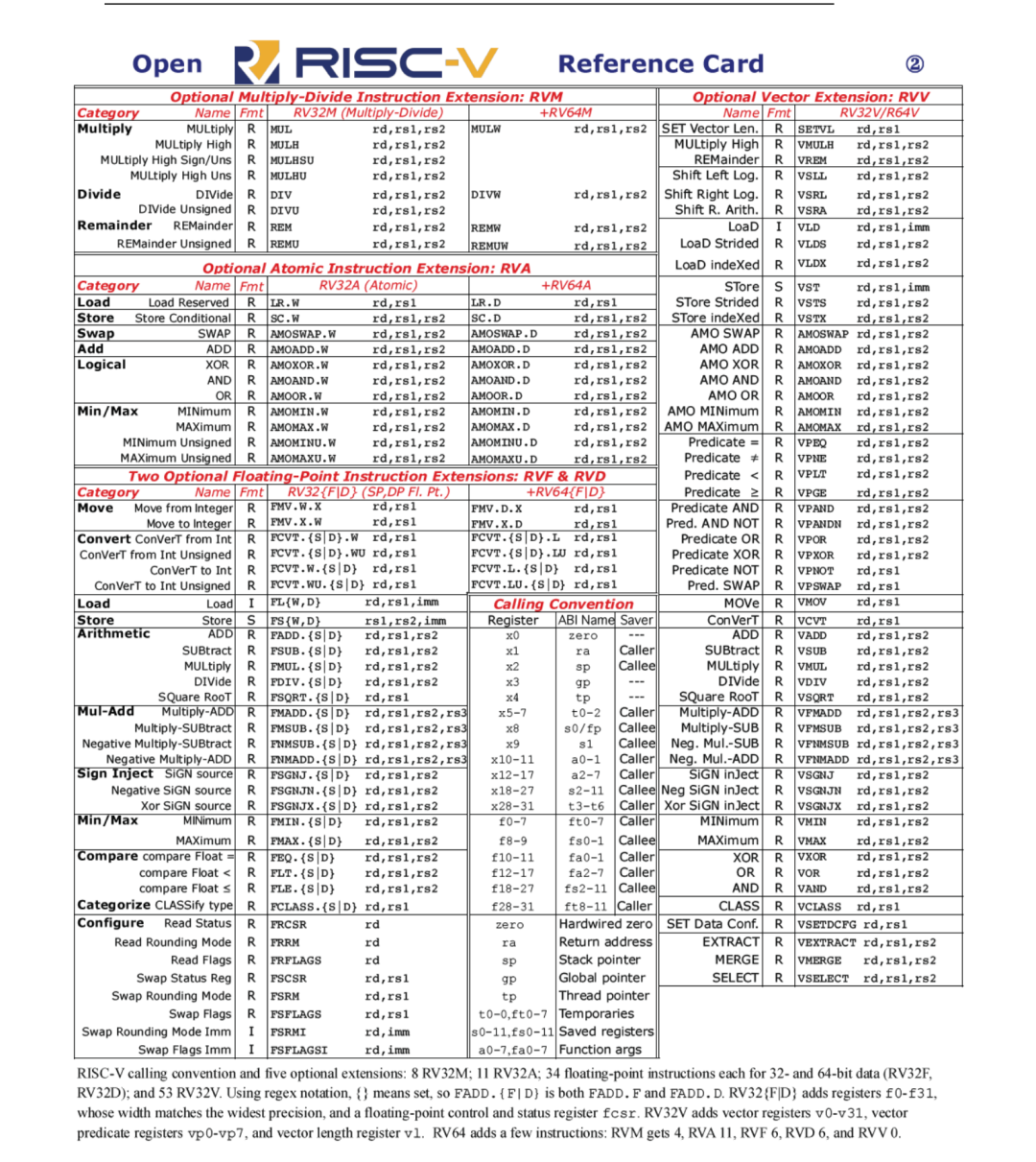

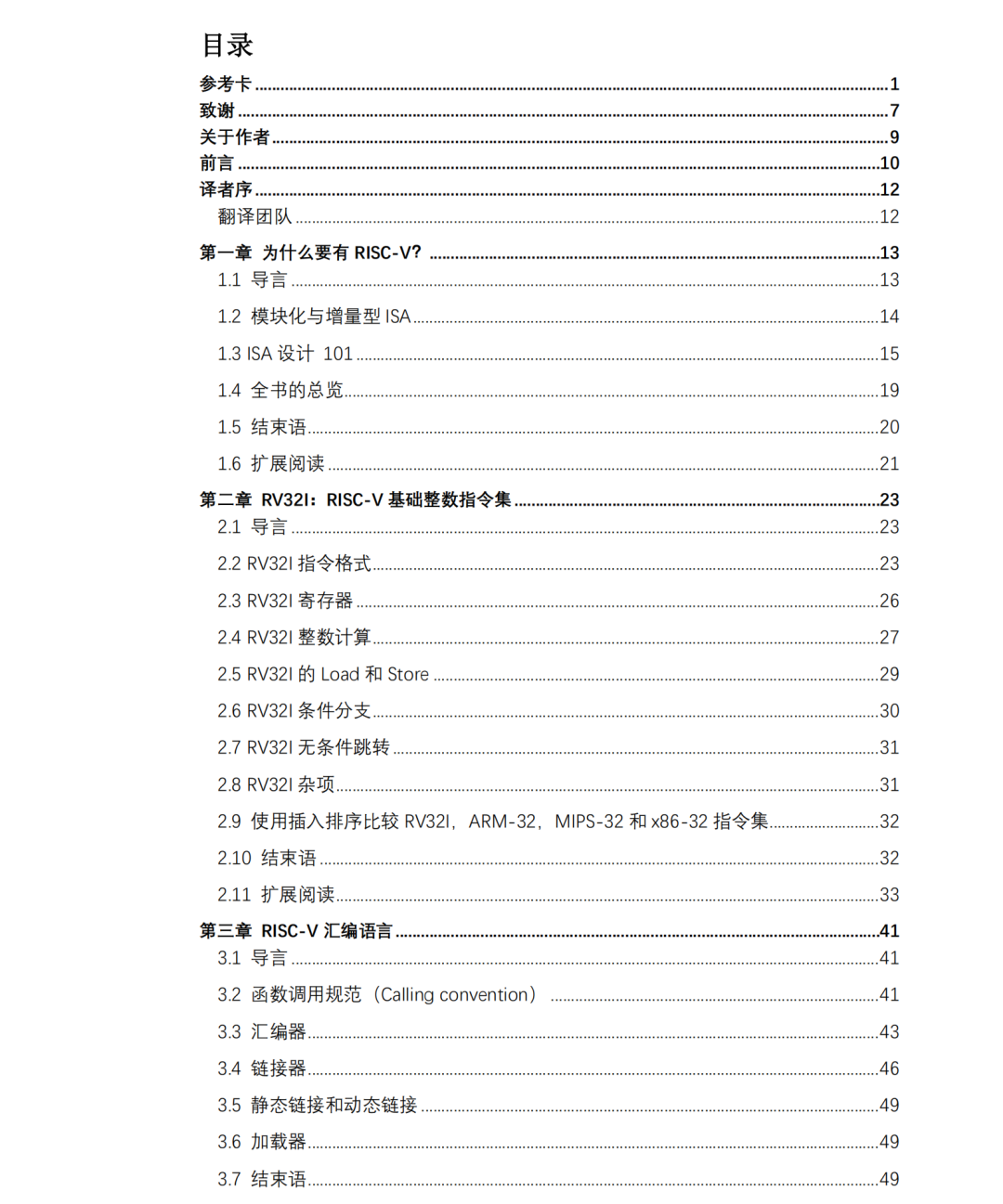

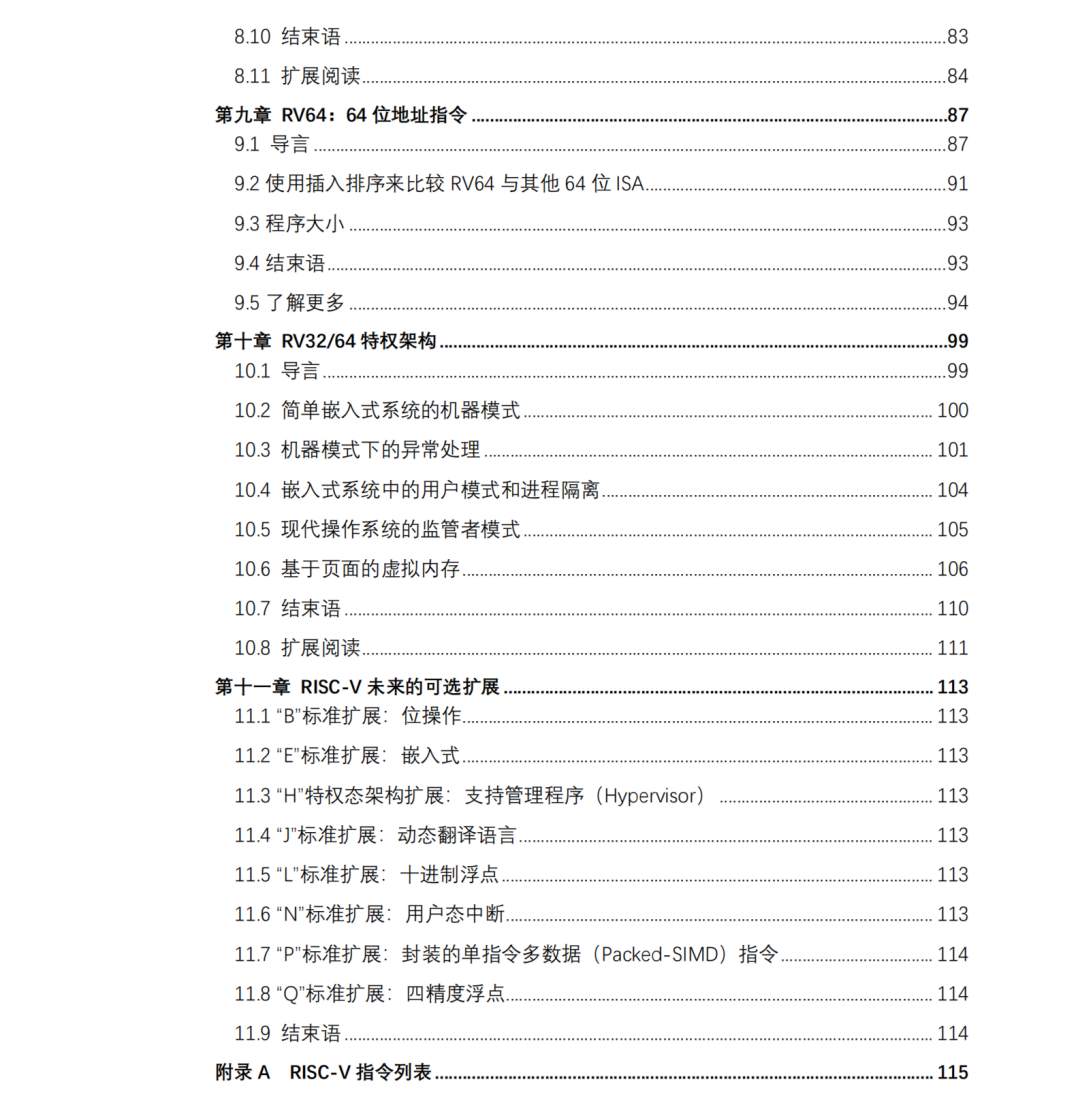

RISC-V更多技术内容,请参看《RISC-V手册开源指令集指南》,十一章技术干货,目录如下所示:

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。