聊一聊华为 Mate 60 的事情

2023 年 8 月 29 日,华为 Mate 60 系列开售,华为终端的微博至今仍然置顶此消息。

之后,关于华为的各种讨论和新闻就层出不穷,有一些技术名词可能让好多人十分困惑。今天就跟大家随便聊一聊可能会让你感到困惑的问题。

为什么 Mate 60 这么引人关注?

随着 2018 年美国的各种制裁开始,华为的麒麟芯片就停止了生产,以至于华为 Mate 50 成为了被迫搭载了"性能还可以"的骁龙芯片的 4G 手机。

关注华为的同学一定非常想念 Mate 40 的这颗芯。

但是根据一些国内外科技自媒体和拆机机构的分析,这次的华为 Mate 60 内部再次搭载了麒麟芯片(9000s),而且很可能是 7nm 制程工艺的芯片。

那么如果这款 Mate 60 内部搭载的麒麟 9000s 确实是 7nm 制程工艺,那就说明至少在 7nm 晶圆生产研发这个领域已经可以一定程度上摆脱美国制裁的影响。

当然,目前的消息都只是猜测,也都比较敏感,所以我们不做过多分析,等待官方消息即可。

麒麟芯片不是咱们自己设计的吗,为什么会受制裁?

麒麟芯片确实是华为海思设计的,但是我们并没有能力把它制造出来,当然准确说是没有能力制造最顶尖制程工艺的芯片。

有人说,那就攻克这个技术呀,我们号称自研的麒麟芯片怎么美国一制裁就搞不出来了呢?能这么想的朋友是对芯片制造流程的难度和世界分工没有概念。

就拿最单一的一个小点来举例。设计一款芯片的电路图后,需要交由晶圆代工厂来制造,你可以简单把晶圆代工厂和台积电划等号,最先进制程工艺的芯片就只有台积电能代工制造,全世界只此一家,剩下的英特尔、三星等都属于其他家。

这么看,台积电已经够牛了,但它使用的目前最先进的光刻机 EUV 却只有荷兰的 ASML 公司才能生产。它们既不设计芯片也不制造芯片,仅仅是提供制造芯片的工具之一光刻机。

从可替代程度来讲,ASML 在光刻机领域的不可替代性要比台积电在晶圆代工领域的不可替代性强更多。

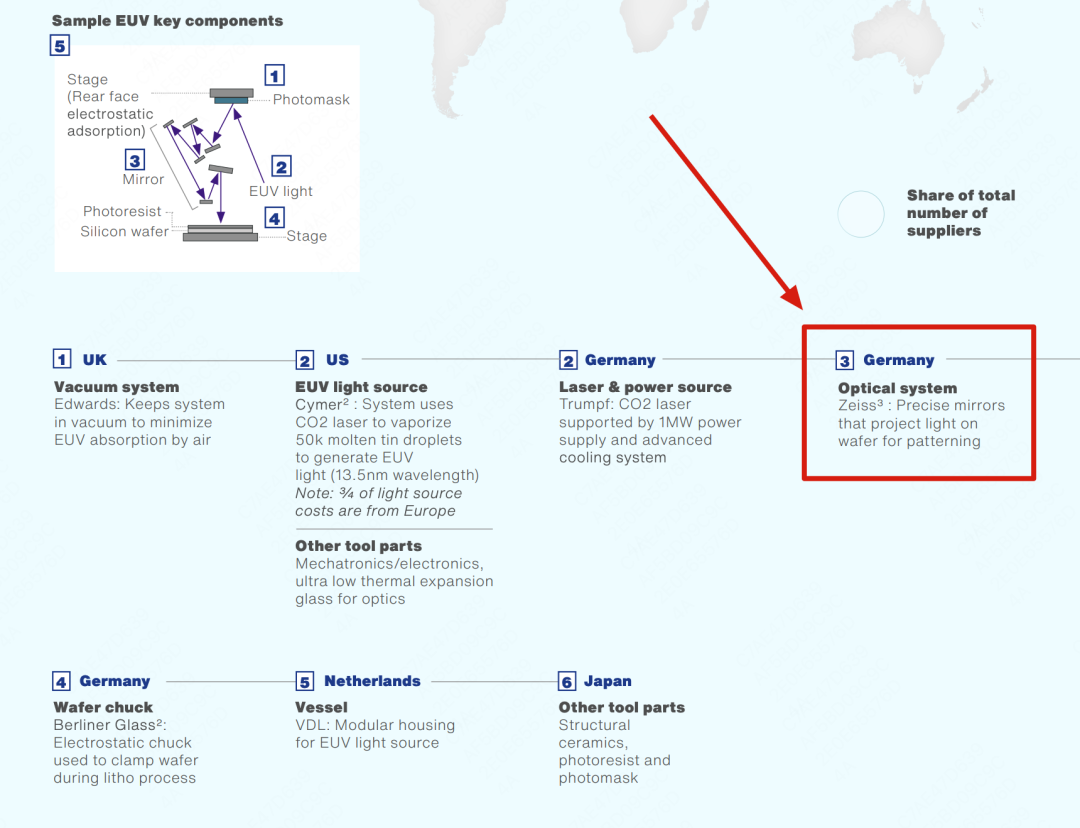

这么看,ASML 够牛了吧?但它的 EUV 光刻机中使用的极紫外光技术必须依赖德国蔡司生产的全世界最光滑的镜头,这又是全世界仅此一家才能生产出来。

除此之外,EUV 光刻机中的其他原材料还依赖一些日本和美国的技术,虽然 ASML 在光刻机领域独领风骚,但其中的一些零部件还是需要依赖其他公司或国家。

所以你可以看到,芯片领域已经卷到了什么程度,台积电制造芯片,荷兰 ASML 给台积电提供制造芯片的工具,德国蔡司给 ASML 提供制造制造芯片的工具的工具。

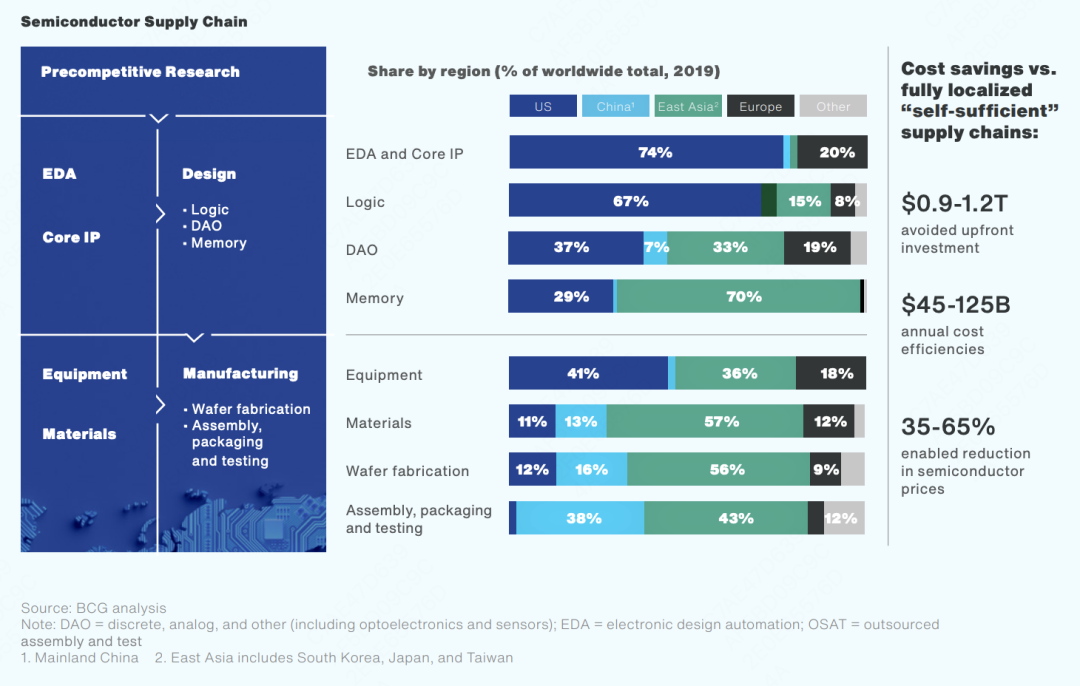

即便是你想 all in 只做芯片流程中的很小的一环,也很难做到完全自给自足,因为所需要的技术以及工艺上的精度要求简直太苛刻了。这世界上没有任何其他领域的供应链如此复杂,需要全世界一起来参与。

所以我打个比方,只要德国蔡司镜头中有一个小技术或者小专利用到了美国的技术,美国就可以对其进行限制,没有蔡司镜头就没有 EUV 光刻机,没有 EUV 光刻机就没有台积电 5nm 工艺,没有 5nm 工艺当时 Mate 40 的麒麟 9000 芯片就只能设计个图纸但造不出来。

要想真正摆脱制裁,就要打通整个流程中的每一环,而这其中哪怕一个很小的蔡司镜头,可能都需要倾尽一个公司或一个国家的财力和时间来打造,还不一定能有成果。

如果我们有个天才,突破了这里面的所有技术,能真正摆脱制裁吗?

不能,因为这不单单是技术难度的问题。

就算用超级黑科技打通了芯片设计的后面的全部芯片制造环节,可是芯片设计的前面还有指令集的授权以及芯片设计软件 EDA 的授权问题。

设计一枚芯片,你得用专业的 EDA 软件,并且选择一套指令集架构。

先说 EDA 软件。全世界的 EDA 被三家美国血统的公司垄断。很好理解,假如我们无法使用它们的 EDA 软件,就算我们自己搞,但台积电可能并不认其他 EDA 软件输出的格式,这就不是技术问题本身了。

再说指令集授权。手机芯片通常使用的就是 ARM 公司的 ARM 指令集架构,而且有很多代际版本。即使已经得到 ARM-v8 指令集的授权,但假如 ARM-v9 的授权停止,那么今后只要有 APP 使用了 ARM-v9 中的任何一条新指令,那么在手机上就跑不起来。

你说那我们造一个新指令集呗?难,Wintel 和 AA 联盟生态的影响太大了。

比如龙芯使用的就是自研的指令集架构 loongarch,但搭载龙芯的电脑短时间内肯定是无法普及给老百姓的,举个简单的例子就是说别人发给你一个 word 文档你打不开,很多游戏也玩不了。

所以,不要以为只需要有聪明的大脑和人力物力财力就可以造芯片了,需要考虑的综合问题太多了。

(据说)麒麟 9000s 的 7nm 是什么意思?

不严谨地说,就是芯片上最小的晶体管的尺寸是 7nm,晶体管越小,芯片上能排布的晶体管数量越多,性能越好,功耗也会越低。

再稍稍严谨一点,7nm 指的是晶体管中的栅极(控制电流从源极流向漏极的开关)的宽度。

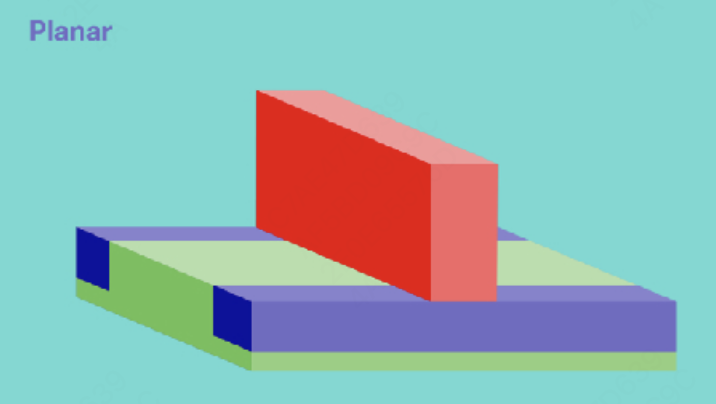

但再严谨一点的话这样说就又不对了。在 22nm 以上的尺寸时,说 XXX 纳米就真的表示晶体管栅极的宽度,是一一对应的。但是到 22nm 以下时,由于再做小栅极宽度就会导致漏电现象发生(量子隧穿效应),所以不能再单纯通过缩小尺寸来进一步提升工艺了。

这就是当时说摩尔定律快要失效了的原因,你总不能把晶体管尺寸设计的比原子还小吧,这已经不是技术工艺突破的问题了,除非咱们人类在基础物理有突破。

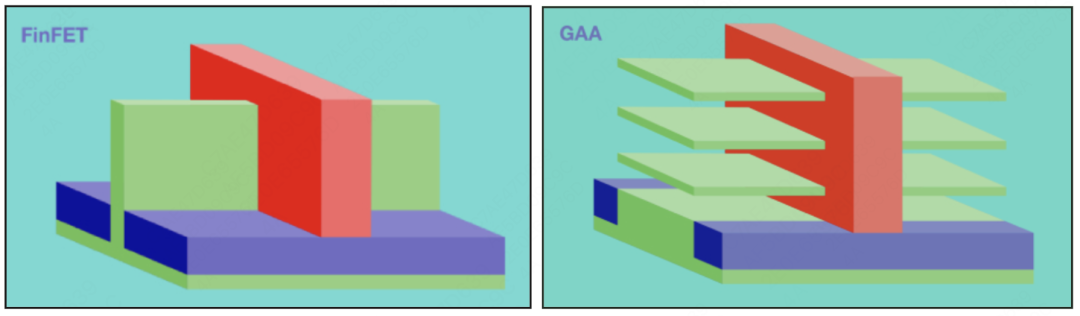

于是人们便通过其他方式改造晶体管形状来让其等效于缩小尺寸,比如 FinFET 和 GAA 技术。之前的那种叫平面晶体管,现在的这些与之相对应叫 3D 晶体管,还是很形象的。

具体原理我也不懂,但是此时的 7nm 5nm 3nm 已经不再是单纯地表示晶体管栅极宽度了,仅仅是其性能提升和功耗降低的效果可以等效地认为和理论上把栅极宽度做到了 7nm 5nm 3nm 一样。

从 7nm 进化到 5nm 是不是很容易?

我们可能很自然地认为,从 14nm 突破到 7nm 都成功了,那再从 7nm 突破到 5nm 不是随便玩玩的事儿么?

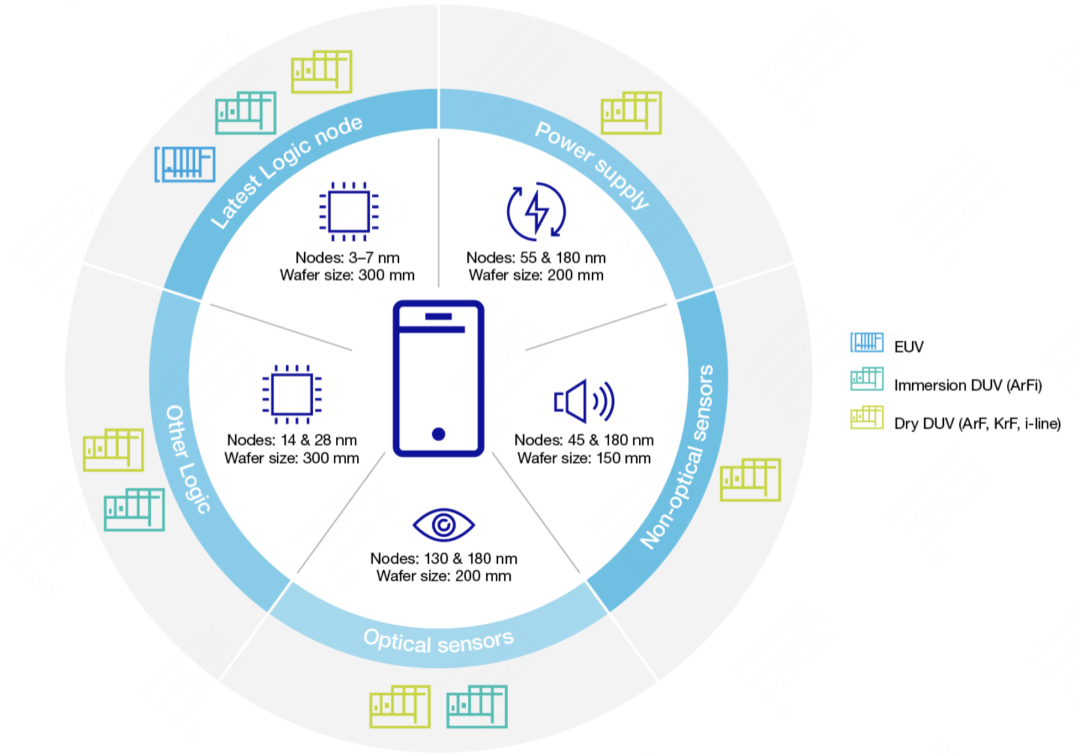

不是的,这就要从光刻原理说起了。其实 ASML 的官网上就有对芯片制造和光刻原理的系统性介绍,并且非常亲民,感兴趣的朋友可以看一遍。

我就用相对比较 low 的语言给大家通俗讲一下。

光刻就是用光在芯片上画画。举个夸张的例子,假如芯片足够大,里面需要的电路也不复杂,我们也可以用铅笔在上面手画。只不过,芯片的尺寸太小了,只有光才能达到那么精细的程度,也只有纳米(nm)这个单位才配得上描述这个制程。

光的波长越小,刻画在芯片上的晶体管尺寸也就越小,为什么?别问,问就是。

瑞利准则公式:CD = k1 • λ / NA

所以要想缩小晶体管尺寸,一方面要不断制造波长更短的光,就好比我们把铅笔削尖一样,另一方面可以用一些其他技巧。

比如干式 DUV(深紫外光)光刻机的波长为 193nm,台积电林本坚突发奇想在光前面加一层水使光发生了折射,波长等效变成了 134nm,这就有了浸没式 DUV 光刻机。

拿到 134nm 的光之后,再通过多重曝光等技术,使得最终刻在芯片上的尺寸达到了 7nm(刚说了这里的 7nm 已经不直接表示晶体管栅极宽度了),但这已经是 DUV 光刻机的极限了。而且需要付出很多成本。

我国购买过 ASML 的 DUV 光刻机,但后续可能也要断货了。如果我们能够大量生产 7nm 工艺的芯片,一种方式是我们自研了 DUV 光刻机而不再依赖 ASML 是否卖给我们,另一种方式是利用现存的不包售后的几台 DUV 光刻机大量生产,但要解决机器磨损的问题。

ASML 目前最先进的光刻机是 EUV(极紫外光)光刻机,光的波长直接缩短到了 13.5nm,同样制作 7nm 芯片对比 DUV 光刻机需要用各种花里胡哨的技巧来说,属于降维打击,成本也更低。

同时还能制造出 DUV 光刻机无法企及的 5nm 和 3nm 工艺。

所以从 14nm 突破到 7nm 和从 7nm 突破到 5nm 并不是单纯数字表面看起来的难度。我们当然可以用 0.5mm 粗的铅笔头画出 0.1mm 的线条,但和我们直接使用 0.1mm 的铅笔画是完全不同的概念。

如果我们可以造出 EUV 光刻机并且用它来生产 7nm 工艺的芯片,那和使用 DUV 并用极大的成本很极限地制造 7nm 的芯片,又是不同的意义了。

说句题外话

昨天我发布了一篇文章,但可能因为触发了一些关键字导致文章被删除。我看了评论区的一些评论,感觉很多人戾气还是太重了。

不要一味地相信某件事,也不要一味地怀疑某件事,芯片领域的故事错综复杂,涉及到技术、专利、政治、经济、生态等多方面因素,远比咱们想象的要复杂得多,我们尽量冷静和理性地分析问题。

最后,最近因为查阅资料发现了一本爽文小说《从获得十五台光刻机开始》,大概两三年前写的吧,本来是个穿越爽文,但却意外地把当今芯片的格局写的十分准确且生动,感兴趣可以看一看。