关于SPI,你知道的和不知道的都在这里

关注、星标公众号,直达精彩内容

文章来源:https://www.engineersgarage.com/tech-articles/spi-what-is-serial-peripheral-interface-protocol/

整理:技术让梦想更伟大 | 李肖遥

SPI在嵌入式系统中非常普遍。无论是芯片上的系统处理器(如ARM、MIC或Power PC等高端32位处理器)还是微控制器(如AVR、PIC等),通常包括能够以主从模式运行的SPI控制器。系统内可编程AVR控制器可以使用SPI接口编程;基于芯片或FPGA的设计有时使用SPI进行通信。当我们想要与外围设备快速传输数据,并对实时性有要求时,SPI是目前常用的一种技术。除SPI外有许多串行接口,如Morse电报、RS232、 USB、火线、以太网等,对于许多设计来说,每个串行接口都有其优缺点,如何选择取决于所需的数据速率、空间可用性和噪声考虑等因素。

SPI即串行外围接口,用来取代并行接口,这样设计时就不必绕着PCB布线并行总线了。它提供设备之间的高速数据传输,摩托罗拉是第一家将SPI命名为电路技术的公司,该技术应用于上世纪70年代末的首个基于68000的MCU,用于连接周边设备,后来被业内其他公司采用。接口的简单性和速度使通信或传输数据变得容易,并使其成为流行的通信协议。

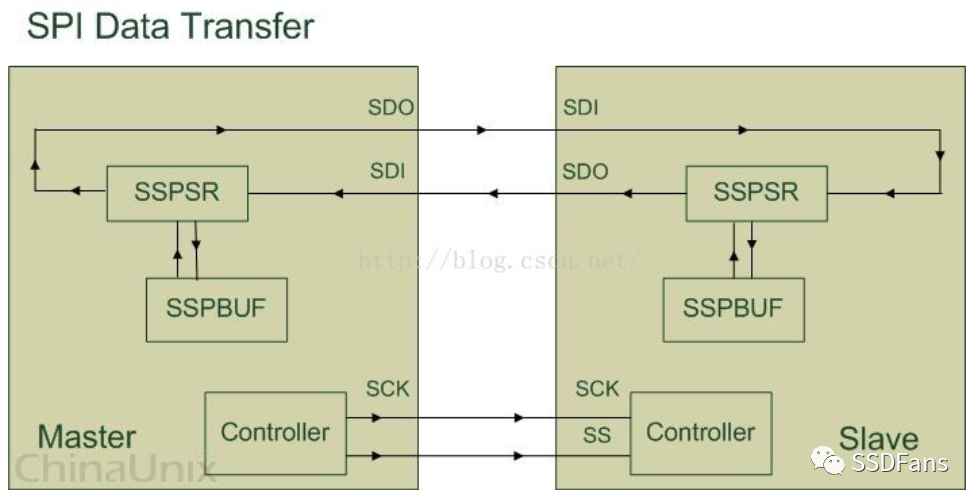

SPI是一个简单的4线串行通信接口,使控制器和外设之间能够相互通信。在SPI中,数据每个时钟周期1 bit速率输入/输出,数据在主设备和一个或多个从设备之间短距离、高速传输。它基于一个8位移位寄存器将数据移出到一个输出引脚,并从另一个输入引脚将数据移入。SPI的另一个特性是,它没有传输总线所有权的概念,即改变主节点,也没有从节点地址。SPI是一种更简单的协议,因此工作频率可以高于10MHz(比TWI的频率高)。

SPI得到广泛使用的一些特性是:

全双工通信;

吞吐量高于TWI;

传输时不限于8位字;

简单的硬件接口;

可随意选择消息大小、内容和目的;

通常符合低功耗要求;

从机使用主机产生的时钟,不需要精确的振荡器;

由于电路较少,功耗要求比TWI低。

然而,将TWI串行接口与SPI进行比较是不公平的。它们有各自的应用领域,这取决于系统的需求。TWI有如下特性:

IC封装上的引脚数比SPI少;

存在硬件流控制;

它有一个正式的标准,不像SPI;

它在通信之前给出从机地址。

为什么SPI在PCB下应用最多

尽管SPI主要是为主机处理器和外设之间的通信而开发的,但是通过SPI连接两个处理器也是可能的。SPI总线通常只用在PCB上;在PCB领域之外使用SPI有很多阻碍。首先,SPI被设计用来在不同的IC芯片之间以非常高的速度传输数据;由于高速要求,总线的长度不能太长,否则会因为电抗增加而无法使用。当然在PCB外使用低速SPI是有可能的,但这不是很实际。外围设备可以是实时时钟、转换器(如ADC和DAC)、内存模块(如EEPROM和FLASH)、传感器(如温度传感器和压力传感器)或其他设备(如信号混频器、电位器、LCD控制器、UART、can控制器、USB控制器和放大器)。

尽管SPI主要是为主机处理器和外设之间的通信而开发的,但是通过SPI连接两个处理器也是可能的。SPI总线通常只用在PCB上;在PCB领域之外使用SPI有很多阻碍。首先,SPI被设计用来在不同的IC芯片之间以非常高的速度传输数据;由于高速要求,总线的长度不能太长,否则会因为电抗增加而无法使用。当然在PCB外使用低速SPI是有可能的,但这不是很实际。外围设备可以是实时时钟、转换器(如ADC和DAC)、内存模块(如EEPROM和FLASH)、传感器(如温度传感器和压力传感器)或其他设备(如信号混频器、电位器、LCD控制器、UART、can控制器、USB控制器和放大器)。

SPI协议

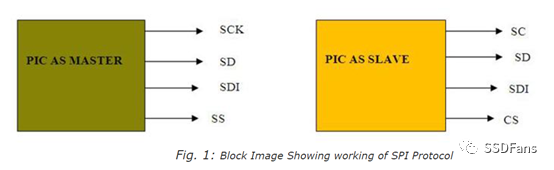

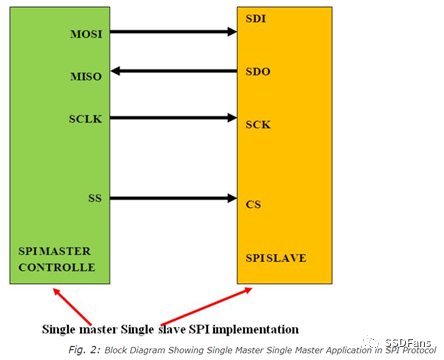

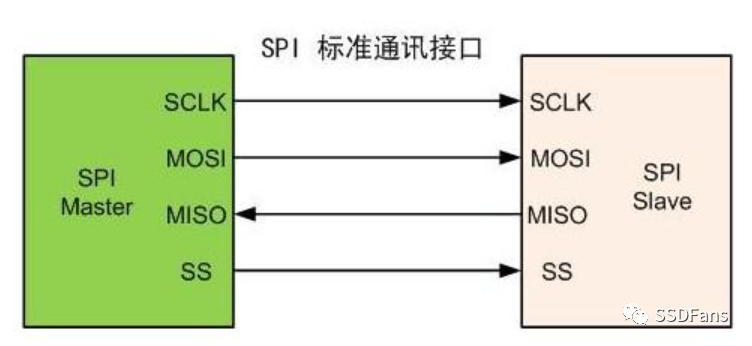

SPI协议包括以下4条信号线:

MOSI (Master Out Slave In)

MOSI信号由Master产生,接收端是Slave;

MISO(Master In Slave Out)

Slave产生MISO信号,接收方为Master;

SCLK/SCK

SCLK由master产生,用于在master和slave之间同步数据传输;

SS/CS

SS信号由master产生,用于选择单个slave。

有时串行数据输入[SDI]被用于MOSI,串行数据输出[SDO]用于MISO。

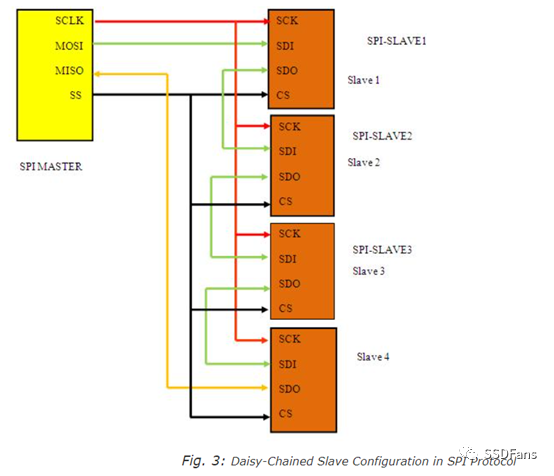

一个主控制器可以与多个SPI外设通信,一般有两种设置方法:

1. 级联slave配置;

2. 并行slave配置。

级联slave配置

级联slave是将所有的时钟线(SCLK)和片选(CS)连接在一起。数据通过微控制器传输到每个外设,最后再返回到微控制器。前一个slave的数据输出连接到下一个slave的数据输入,从而形成一个更宽的移位寄存器。因此,级联slave被视为一个更大的设备,他们连接相同的芯片选择信号。这意味着master只需要产生一条SS线,而不用为每个slave都产生一条单独的SS线。

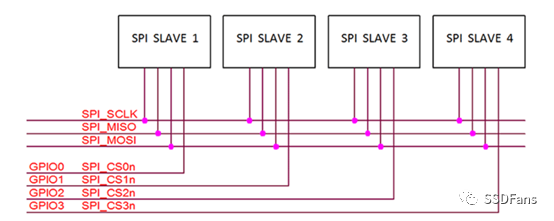

并行slave配置

这是典型的SPI总线配置,包含一个master和多个slave。在这个独立或并行的从属配置中:

所有时钟线(SCLK)都连接在一起;

所有MISO数据线都连接在一起;

所有MOSI数据线都连接在一起。

SPI通信

SPI通信一直是由master发起的。首先master产生时钟,时钟频率小于或等于slave支持的最大频率;随后master通过产生时钟信号(SCLK)来控制数据传输,并通过将特定slave的芯片选择(SS)线拉低来进行通信。总线上的slave如果没有被master选中,将会忽略来自主机的输入时钟和MOSI信号,并且绝对不能驱动MISO;这意味着master每次只选择一个slave。

四个引脚的使用取决于设备。例如,某些设备不需要输入(例如ADC), SDI引脚可能不存在,或者有些设备不需要输出(例如LCD控制器),SDO引脚可能不存在。如果一个微控制器只需要与1个SPI外设通信,那么该slave上的CS引脚可以接地(CS低电平有效)。对于多个从设备,每个从设备都需要一个独立的CS信号。

SPI中三态输出的意义是什么?

在数字电子学中,三态逻辑允许输出端口除了0和1逻辑电平外,还采用高阻抗状态。这允许多个电路共享一个输出线,大多数外设都有三态输出,当设备未被选中时,输出会进入高阻抗状态(断开)。没有三态输出的设备不能与其他设备共享SPI总线。

SPI设备有时使用另一条信号线向主机CPU发送中断信号。使用中断信号例子有温度传感器的温度警报,实时时钟芯片发出的警报,以及手机声音编解码器监测到的耳机插孔插入等。

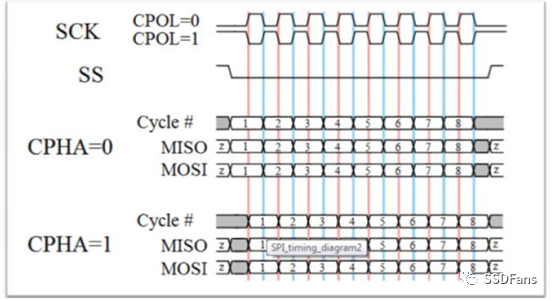

时钟极性和相位

另一对参数称为时钟极性(CPOL)和时钟相位(CPHA)决定了数据驱动和采样的时钟信号的边缘。除了设置时钟频率,master还必须配置时钟极性(CPOL)和相位(CPHA)。由于时钟作为数据通信的同步,在这个CPOL和CPHA的基础上,有四种可能的模式可以在SPI协议中使用。

SPI应用

全双工能力使得SPI对于主/从应用场景下十分高效,通过全双工模式可以为数字音频、数字信号处理等应用实现高效、快速的数据流。SPI用于与各种外设通信,例如:

传感器

温度,压力,ADC,触摸屏,视频游戏控制器;

控制设备

音频编解码、数字电位器、DAC;

相机镜头

佳能EF镜头支架;

通讯

以太网,USB, USART,CAN手持视频游戏;

存储器

Flash和EEPROM;

实时时钟;

LCD,有时甚至用于管理图像数据;

任何MMC或SD卡(包括SDIO变体);

对于高性能系统,FPGA有时使用SPI作为主机的从机接口,使用SPI作为传感器的主机接口,或者用于flash memory的导入接口。

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧ END ‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

关注我的微信公众号,回复“加群”按规则加入技术交流群。

点击“阅读原文”查看更多分享,欢迎点分享、收藏、点赞、在看。