英特尔3nm晶体管密度曝光:超越台积电2nm,碾压IBM 2nm

众所周知,台积电和三星早在去年就已经量产了5nm制程工艺,相比之下英特尔还停留在10nm制程,其最新的7nm工艺今年一季度才正式流片,可能要等到2023年才能面世。

这里需要指出的是,虽然台积电和三星的“5nm”制程工艺的数字要比英特尔的“7nm”制程工艺更小,但是这并不代表英特尔的7nm制程工艺要落后于台积电和三星的5nm制程。因为英特尔的制程工艺节点的命名,此前大多都是严格按照摩尔定律来命名的,即每两年升级一代,新一代的制程命名数字是上一代的0.7倍,对应的晶体管的密度刚好是上一代的约两倍左右。虽然,有一些工艺节点的命名并不是上一代的0.7倍,但是其晶体管密度基本也都保持在上一代的2倍左右。

相比之下,三星和台积电两家厂商为抢占晶圆代工市场,在多年前就开始玩起了数字游戏(比如三星的14nm),即制程工艺节点的命名不再按照摩尔定律的规则来命名,新一代的制程工艺的晶体管密度根本达不到上一代的两倍,甚至只有上一代的不到1.5倍。经过数代的累积,这也使得在同样的制程工艺节点下,台积电、三星的晶体管密度远低于英特尔。

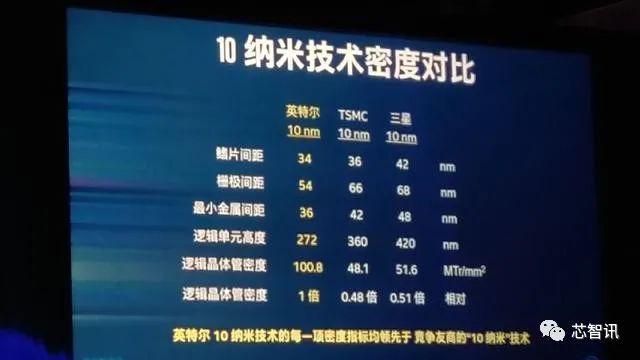

根据此前英特尔公布的数据就显示,台积电10nm工艺的晶体管密度只有英特尔10nm制程的0.48倍,三星10nm的晶体管密度只有英特尔10nm的0.51倍,并且在鳍片间距、栅极间距、最小金属间距、逻辑单元高度等方面,英特尔的10nm制程也是更具优势。基于此,业界也普遍认为,英特尔7nm制程将与台积电和三星的5nm制程相当。

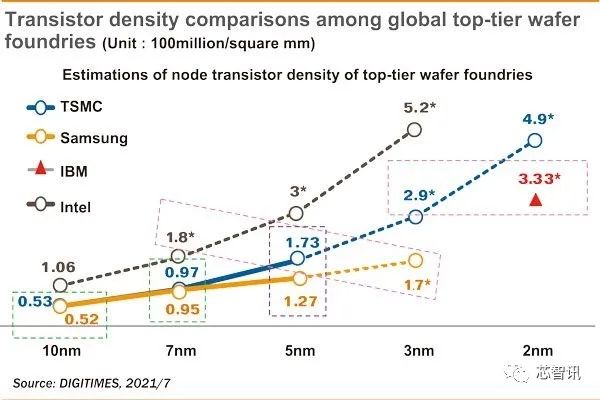

近日Digitimes发布的研究报告,也分析了台积电、三星、Intel及IBM四家厂商在相同命名的半导体制程工艺节点上的晶体管密度问题,并对比了各家在10nm、7nm、5nm、3nm及2nm的晶体管密度情况。

具体来看,在10nm节点,三星的晶体管密度只有0.52亿个/mm²,台积电是0.53亿个/mm²,英特尔已经达到了1.06亿个/mm²。英特尔的晶体管密度达到了台积电和三星的两倍左右。

在7nm节点,三星的晶体管密度是0.95亿个/mm²,台积电是0.97亿个/mm²,而英特尔预计将达到了1.8亿个/mm2。英特尔的晶体管密度依然比台积电和三星高出了80%以上。

在5nm节点上,三星的晶体管密度提升到了1.27亿个/mm²,台积电则达到了1.73亿个/mm²,英特尔将达到3亿个/mm²。英特尔的晶体管密度比台积电高出了超过73%,达到了三星2.36倍。

到了3nm节点,台积电的晶体管密度大约是2.9亿个/mm2²,三星只有1.7亿个/mm²,英特尔将达到5.2亿个/mm²。英特尔的晶体管密度比台积电高出了超过79%,达到了三星2倍以上。即便是英特尔的5nm制程,其晶体管密度也达到了三星2nm的1.76倍。

至于2nm节点,目前没多少数据,IBM之前联合三星等公司发布的2nm工艺密度大约是3.33亿个/mm²,台积电的目标则是4.9亿个/mm²,均低于英特尔3nm的晶体管密度。

虽然以上数据其实不能100%反映各家的工艺技术水平,因为还需要考虑到其他的例如鳍片间距、栅极间距、最小金属间距、逻辑单元高度、功耗、成本等方面的问题。但就摩尔定律关注的晶体管密度指标来看,在同一制程工艺节点上,英特尔的优势巨大,甚至相比台积电、三星更新一代的制程工艺也同样具有一定的领先优势。

编辑:芯智讯-浪客剑

美国将华澜微/格林深瞳/锐科激光等22家中企列入“黑名单”!外交部回应

携手海思研发半导体封装设备?劲拓股份股价大涨20%,证监会发关注函

闻泰科技进军半导体设备领域:安世半导体成立独立半导体设备实体ITEC

官宣!安世收购英国最大芯片制造商!5.64亿元到底值不值?

行业交流、合作请加微信:icsmart01

芯智讯官方交流群:221807116