2022年RISC-V发布四项新规范

RISC-V International 宣布了 2022 年首批四项规范和扩展的批准 — RISC-V Efficient Trace (E-Trace)、RISC-V Supervisor 二进制接口 (SBI)、RISC-V 统一可扩展固件接口 (UEFI) 规范,以及 RISC-V Zmmul multiply-only 扩展。此消息基于 2021 年的势头,其中代表 40 多个扩展的 16 个规范获得了批准。

RISC-V合集:

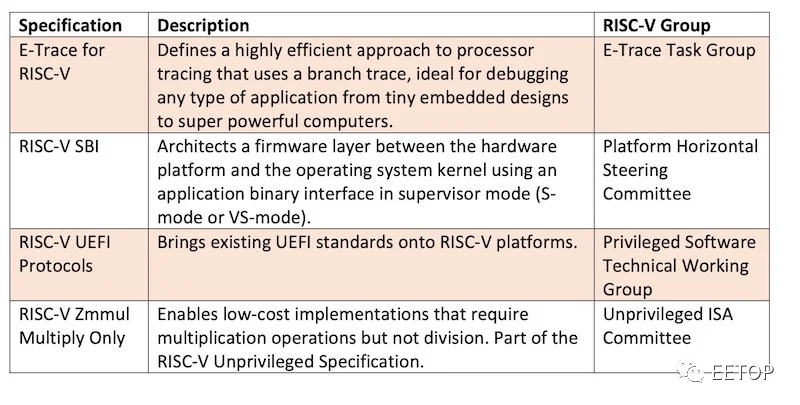

表 1.这里总结了新批准的四个规范,以及负责每个规范的 RISC-V 任务组。所用信息由RISC-V International提供

在本文中,我们回顾了四个新的 RISC-V 规范,分享了我们对 RISC-V International 首席技术官 Mark Himelstein 的采访中的分析,并检查了 SiFive 新版本 X280 RISC-V 处理器的详细信息。

RISC-V 的 CTO Mark Himelstein 介绍称,这些新规范加速了嵌入式和大型系统设计。“调试是芯片上最难做的事情之一,用于 RISC-V 的 E-Trace 创建了一种一种标准的处理器跟踪方式,非常高效且在嵌入式系统设计中特别有用。RISC-V SBI 为开发人员提供了同样重要的资源。在所有 RISC-V 实现中移植 supervisor-mode 软件的能力,基本上允许开发人员编写一次代码就能在任何地方应用。”

“UEFI 现在已经是许多计算机系统的关键元素,在某些应用中,它可能会取代基本的 BIOS 软件。对于许多微控制器应用来说,除法运算的频率太低,不足以证明 divider 硬件的成本是合理的;RISC-V Zmmul 扩展则将特别有利于简单的 FPGA soft cores。”

E-Trace for RISC-V 定义了一种使用分支跟踪的高效处理器跟踪方法,非常适合调试从微型嵌入式设计到超强大计算机的任何类型的应用程序。E-Trace for RISC-V 文档规定了 RISC-V 内核和编码器(或入口端口)之间的信号、压缩分支跟踪算法和封装压缩分支跟踪信息的数据包格式。该规范的开发和批准由 Picocom 的 Gajinder Panesar 和 RISC-V 的 E-Trace 任务组领导。 RISC-V specification for SBI 在 supervisor mode (S-mode or VS-mode) 下使用应用程序二进制接口在硬件平台和操作系统内核之间构建了一个固件层。这种抽象支持跨所有 RISC-V 操作系统的实现都有共同的平台服务。许多 RISC-V 成员已经在他们的 RISC-V 解决方案中实施了 RISC-V SBI 规范,因此批准该规范将确保整个 RISC-V 生态系统的标准方法,确保兼容性。本规范的制定和批准由 Rivos 的 Atish Patra 领导,并在 Platform Horizontal Steering Committee 进行。 RISC-V UEFI Protocols 将现有的 UEFI 标准引入 RISC-V 平台。本规范的开发和批准由 Sunil VL、Ventana Micro 和 Philipp Tomsich、VRULL GmbH 领导,工作在 Privileged Software Technical Working Group 中进行。 RISC-V Zmmul Multiply Only 实现了需要乘法运算而不需要除法的低成本实现,是 RISC-V 非特权规范的一部分。该扩展的开发和批准由 Allen Baum 领导,工作在 Unprivileged ISA Committee 进行。

2022 年的前四个 RISC-V 规范

开放标准组织RISC-V International在 2021 年批准了 16 个规范,代表 40 多个 RISC-V 扩展。今天,该小组正在巩固这些成就,在Embedded World 2022上宣布了四项新规范和扩展批准。公告中还包括一个通知,即针对垂直应用的另外六种规范正在筹备中。

我们将检查每个新批准的规范。每个(除了 Zmmul)都有一个完整的 GitHub 页面,其中包含每个规范的资源。

首先是RISC-V规范的 E-Trace。它阐明了一种有效的处理器跟踪方法。该方案使用分支跟踪,该组织称它非常适合调试任何类型的应用程序——从小型微型嵌入式设计到高性能计算机。

该规范的文档指定了 RISC-V 内核和编码器(或入口端口)之间的信号、压缩分支跟踪算法以及封装压缩分支跟踪信息的数据包格式。Himelstein 表示,E-Trace 是一项至关重要的 RISC-V 功能,可用于调试、故障排除和电路板启动等任务。

(https://github.com/riscv-non-isa/riscv-trace-spec/blob/main/riscv-trace-spec.pdf)

第二个规范,RISC-V for Supervisor Binary Interface (SBI),在硬件平台和操作系统内核之间建立了一个固件层。这被实现为超级用户模式(S 模式或 VS 模式)下的应用程序二进制接口。以这种方式抽象允许跨所有 RISC-V OS 实现的通用平台服务。(https://github.com/riscv-non-isa/riscv-sbi-doc)

SBI 发挥着重要作用。“我不在乎你是否一直在谈论从耳塞到数据中心计算机,”Himelstein 说。“除非你在操作系统和硬件之间有某种接口,否则你无法实现一个系统。”

“系统二进制接口 (SBI) 使操作系统和虚拟机管理程序能够在不了解实施细节的情况下完成工作。SBI 也是构建安全功能的基础,因为您不想直接访问您的内容”重新启动,例如信任根或类似的东西。”

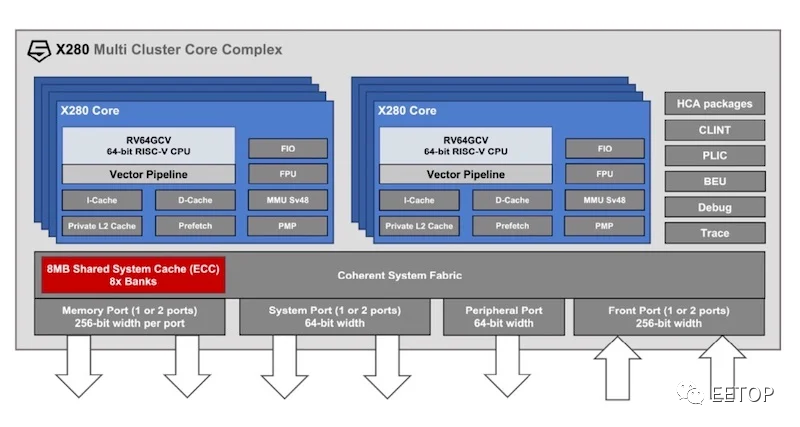

SiFive X280处理器升级瞄准矢量处理

切换到 SiFive 的 Embedded World 公告,该公司发布了其最新版本的 SiFive Intelligence X280 处理器。最初的 X280 版本自 2021 年 4 月开始提供,新的增强功能基于客户反馈。据该公司称,新版本的处理器 IP 增加了主要功能。新功能包括:

可扩展至 16 核高速缓存一致性复合体 “WorldGuard”保护的 SiFive 实施 一个名为 VCIX(向量协处理器接口扩展)的新接口

新的增强型 X280 是一款支持多核和多集群的 RISC-V 处理器,完全支持 RISC-V 矢量扩展标准和 SiFive 智能扩展。它针对边缘的 AI/ML 计算进行了优化,针对 AI 推理、图像处理、数据中心加速和汽车等应用。

RISC-V合集:

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。