外媒:英特尔第一个代工客户确定

共 3778字,需浏览 8分钟

·

2022-02-13 16:01

英特尔EMIB封装深度解读

晶圆级扇出重新分布,使用模塑料的重构晶圆基板作为裸片之间互连的表面(2D)

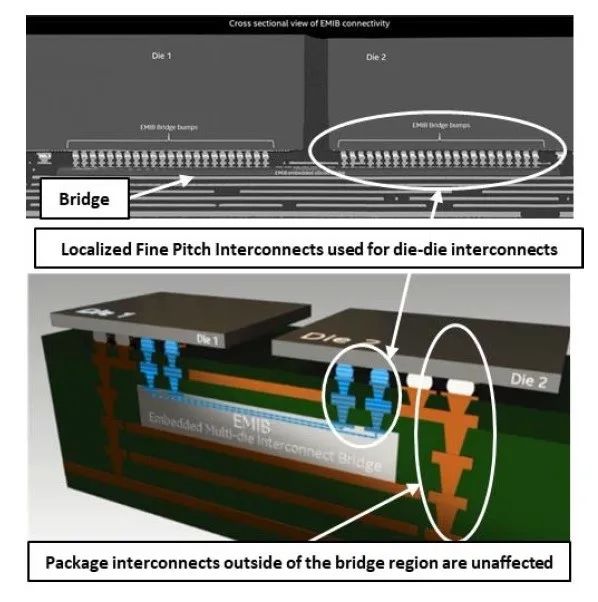

用于重新分配的单独的基于硅的互连层,可以是嵌入有机封装(2.5D)中的全尺寸硅中介层或die到die的硅桥

垂直堆叠的面对面或背对背芯片,利用芯片焊盘的混合键合和直通孔(3D)

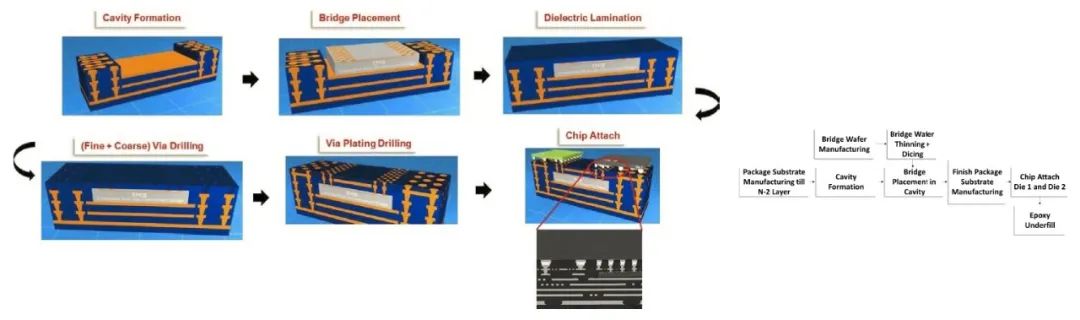

EMIB的制造

EMIB物理实施

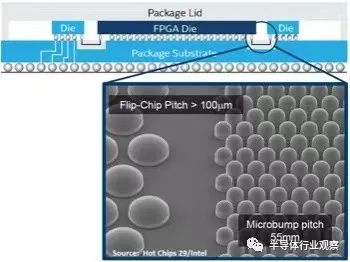

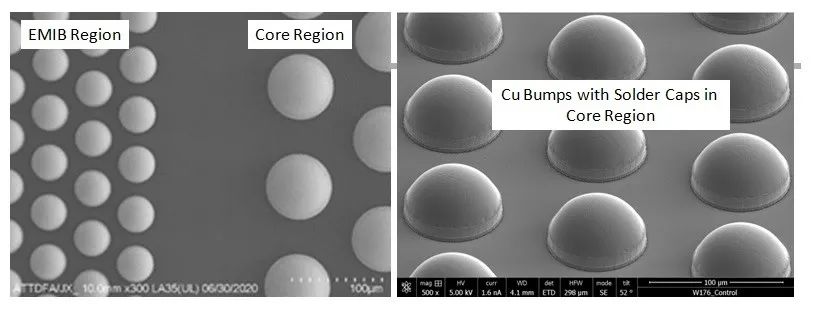

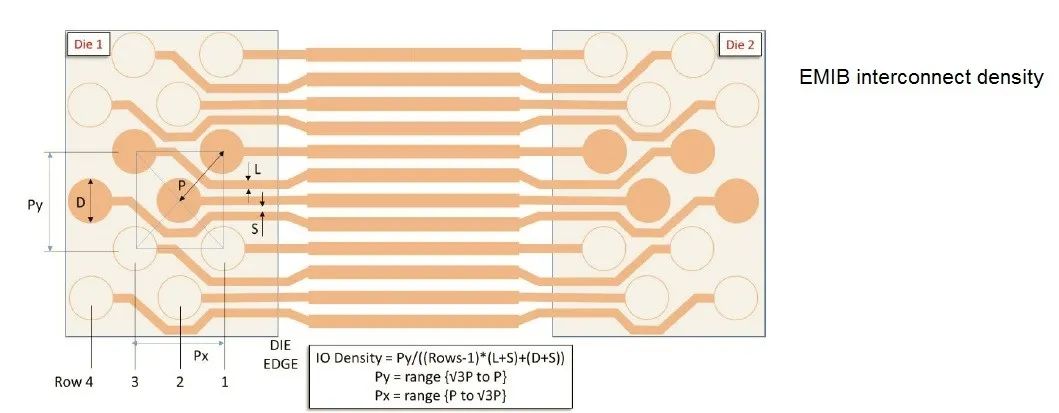

到裸片的凸点间距为55um

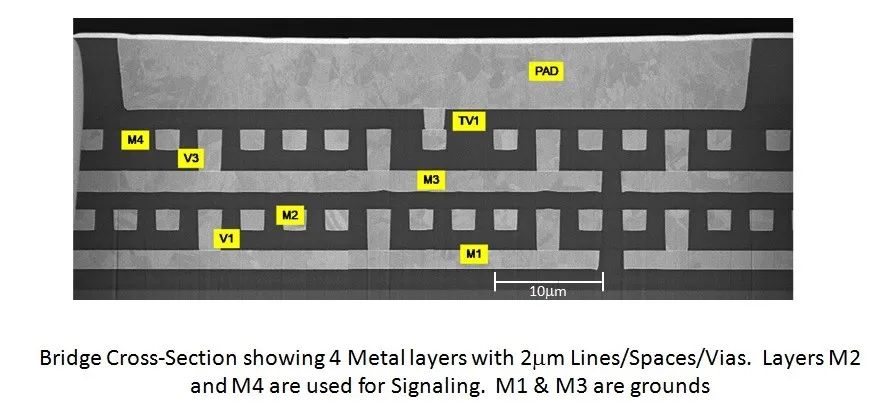

2um线+ 2um间距,金属厚度为2um

4um间距,每毫米“ beachfront”具有250根导线

每个EMIB金属层之间的电介质厚度为2um

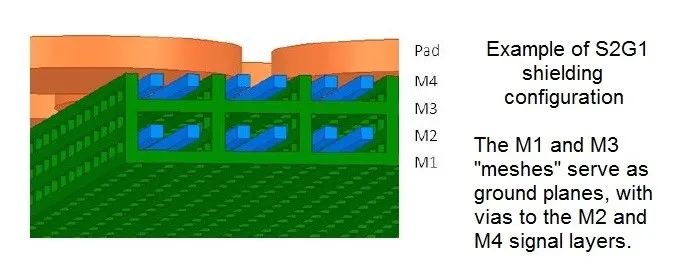

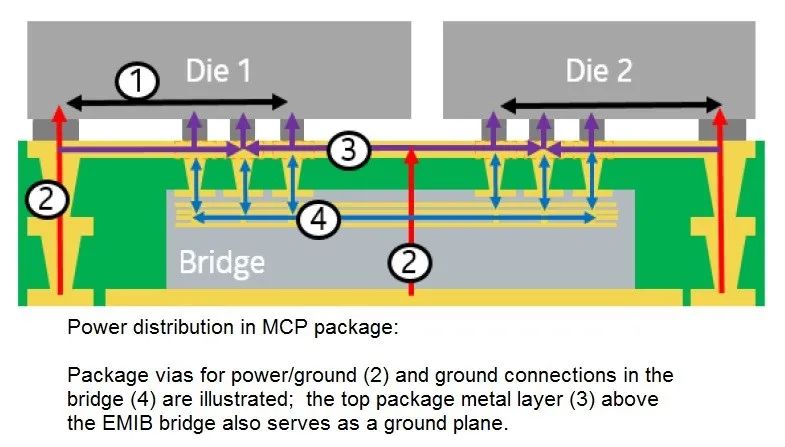

EMIB桥上的4个金属层M1和M3专用于GND平面

通常在M2和M4上利用3信号+ 1接地屏蔽图案的信号层

EMIB电气特性

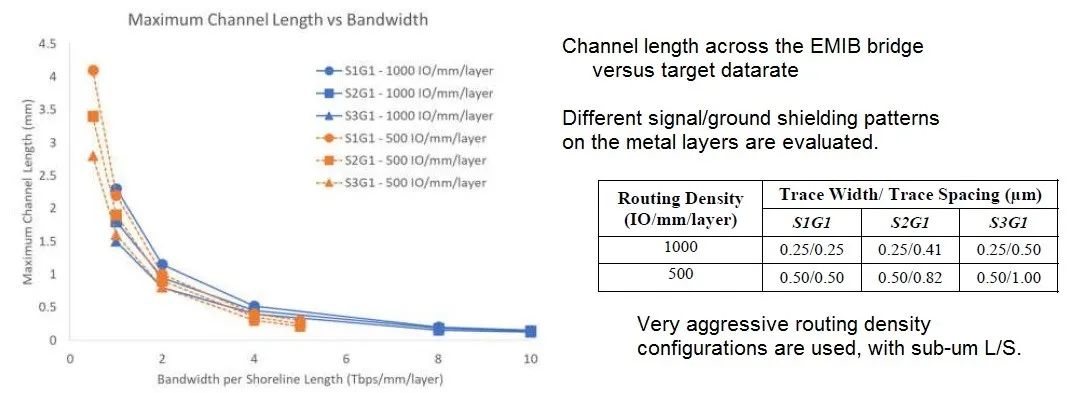

英特尔针对EMIB互连发布了详细的电气分析,评估了各种信号接地屏蔽组合和导线长度的插入损耗和串扰。

一个简单的输出驱动器(R = 50ohms,C = 0.5pF)

无端接的接收器(C = 0.5pF)

四层EMIB金属叠层,介电常数= 4.0

嵌入式桥上方的顶部封装金属平面

1V信号摆幅,具有200mV垂直睁开的接收器灵敏度(为无端接的电容式接收器合并了近端和远端串扰)

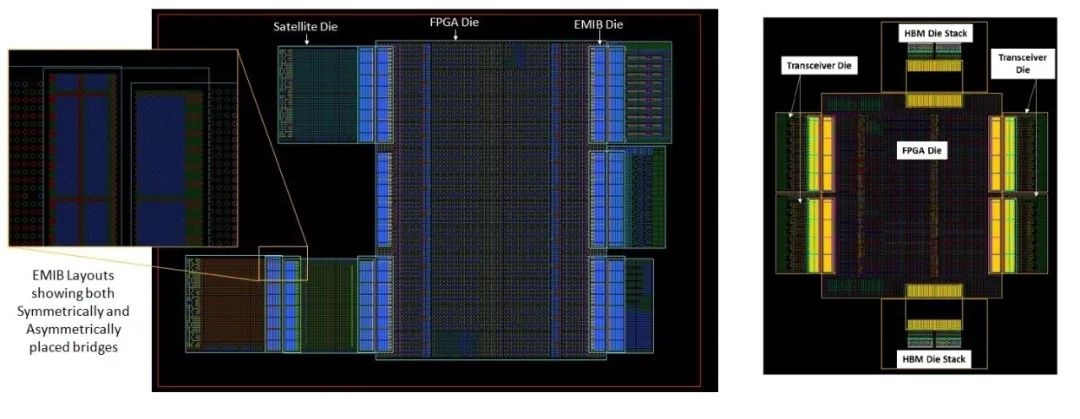

EMIB设计服务

EMIB未来发展

总结

•现有有机包装技术的扩展

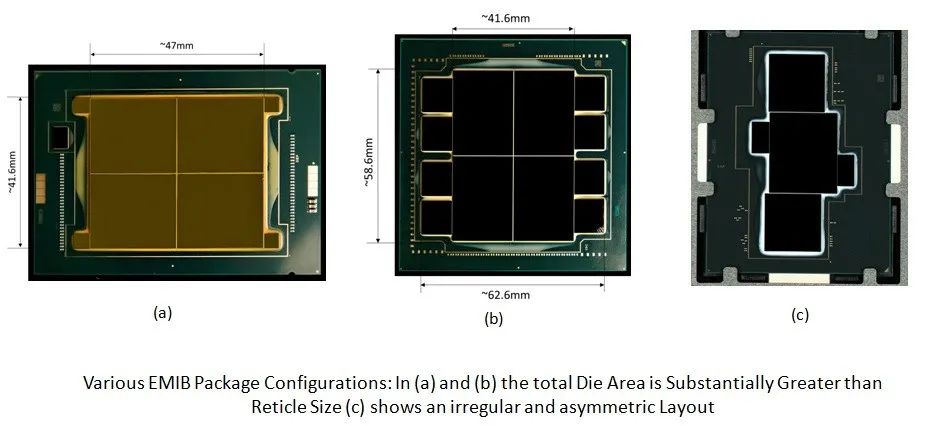

•支持大芯片数和大封装配置

•比全尺寸硅中介层的成本更低

•使用简单的驱动器/接收器电路,支持相邻芯片之间的高数据速率信令

•通过为该链接定制桥来分别优化每个冲模-骰子链接的能力

•芯片凸块和封装组装过程中的额外复杂性

•封装,die和EMIB桥之间的热膨胀系数(CTE)系数不同

注:该内容由“半导体行业观察”综合自semiconductor-digest

原文链接:https://www.semiconductor-digest.com/amazon-aws-is-intel-foundry-services-first-emib-packaging-customer/

美国将33家中国实体列入“未经核实名单”:上海微电子、药明生物、中车等受波及

2021年全球十大半导体采购商公布:华为采购额下滑32.3%,排名跌至第七

未获德国政府批准!环球晶圆收购世创失败:须支付5000万欧元交易终止费

350亿美元!AMD收购赛灵思获中国市场监管总局批准:需履行五大附加限制性条件

164家企业提交机密数据!美国商务部公布半导体供应链调查报告

应届生年薪可达60万?国内芯片人才紧缺的背后:今年芯片行业薪酬涨幅将超50%

行业交流、合作请加微信:icsmart01

芯智讯官方交流群:221807116