超能装!台积电第5代最新封装技术路线图公布

新智元报道

新智元报道

来源:Hardware Info

编辑:Priscilla

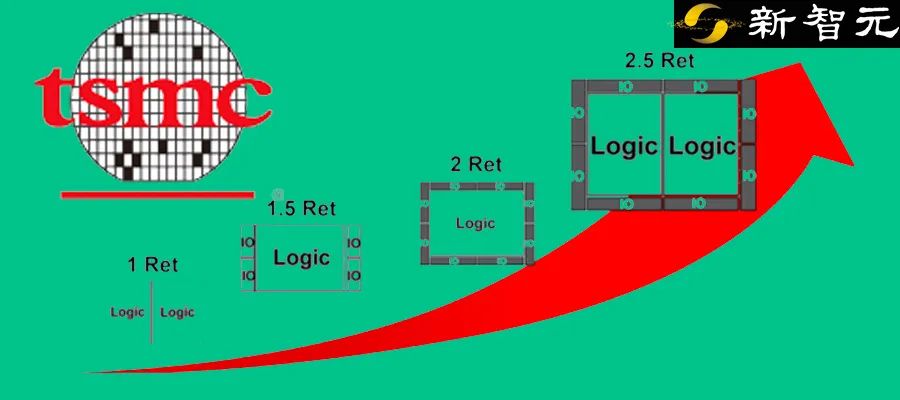

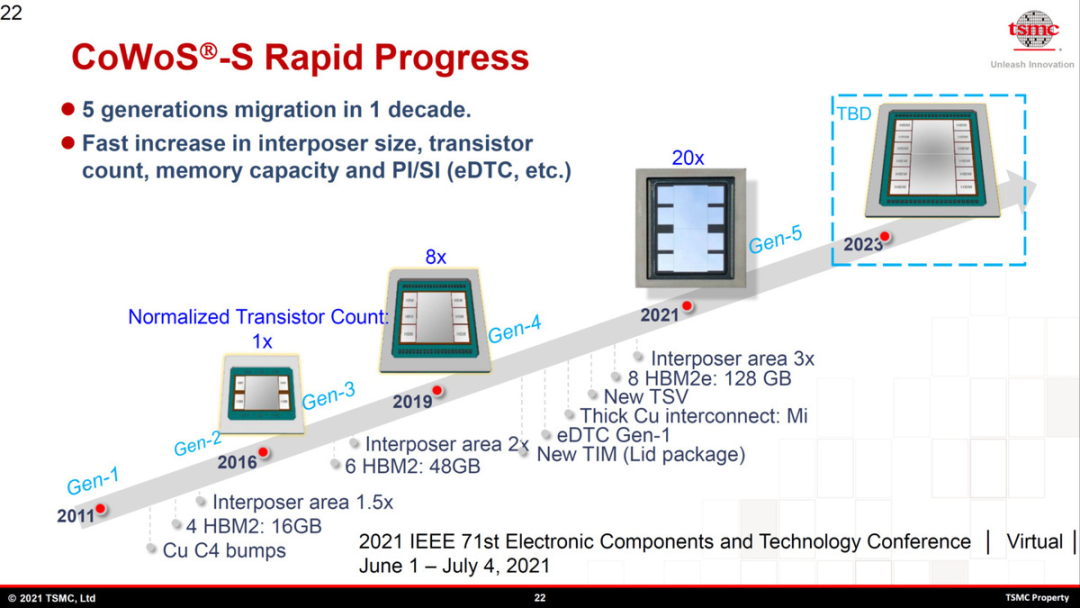

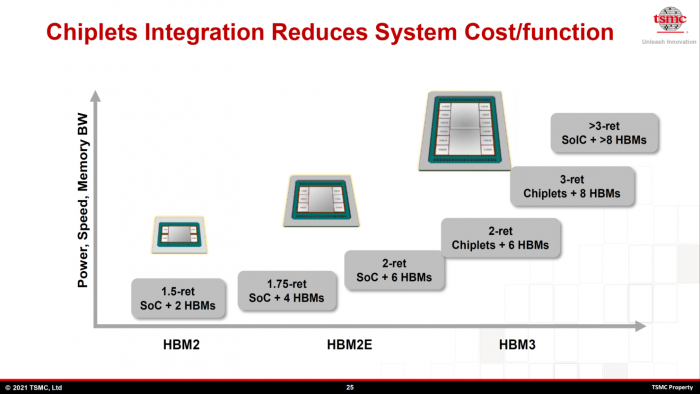

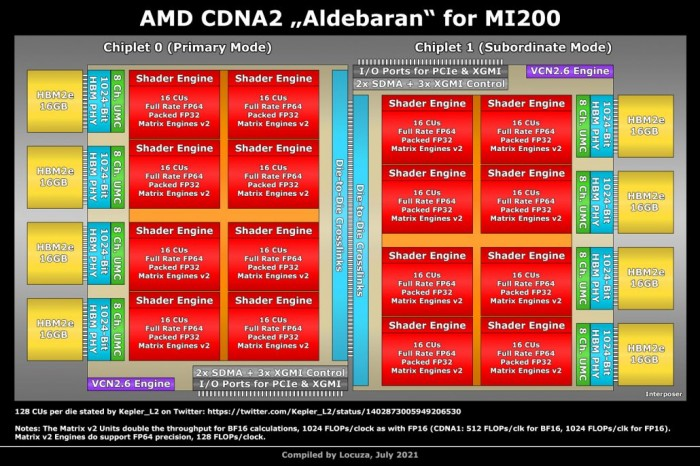

【新智元导读】近日,Hot Chip 33大会在线上举行,台积电在会上介绍了自家封装技术路线图。第5代CoWoS封装技术将于今年晚些时候问世,拥有8个HBM2e堆栈的空间,容量高达128 GB,比第3代技术多存储20倍晶体管,预计2023年发布第6代CoWoS。

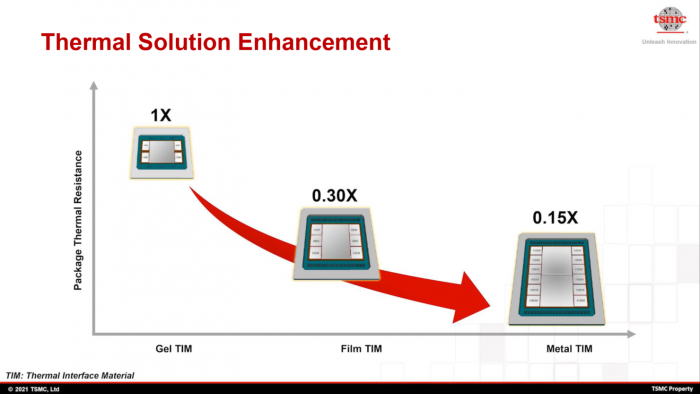

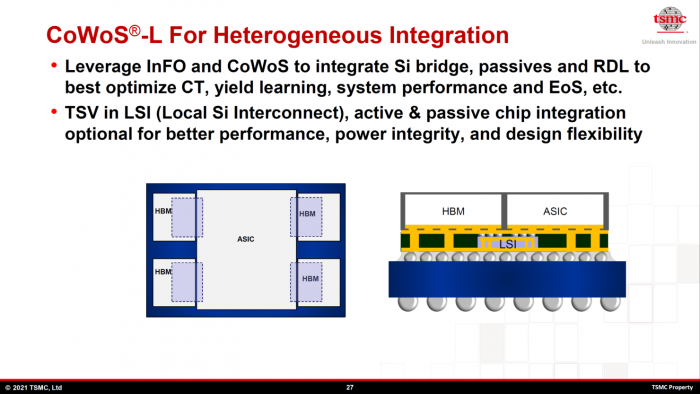

台积电CoWoS封装技术

台积电CoWoS封装技术

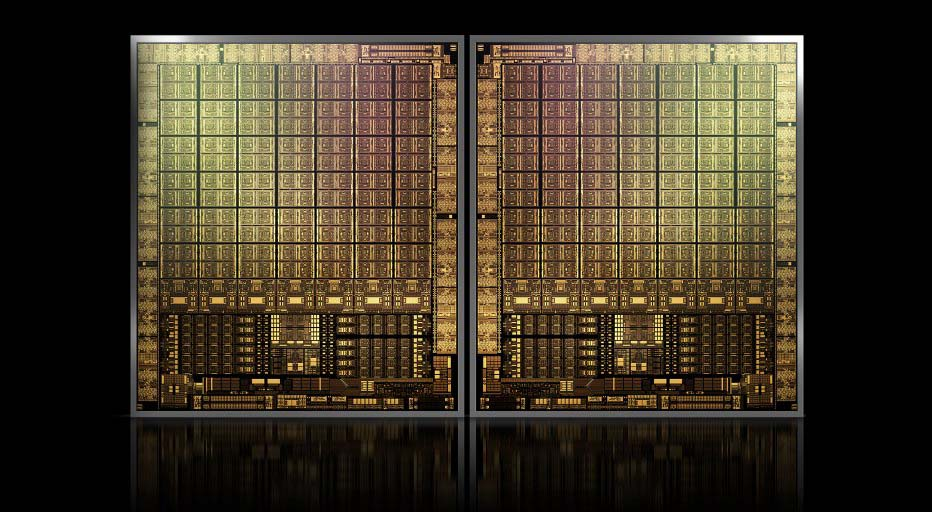

第5代CoWoS封装工艺的应用

第5代CoWoS封装工艺的应用

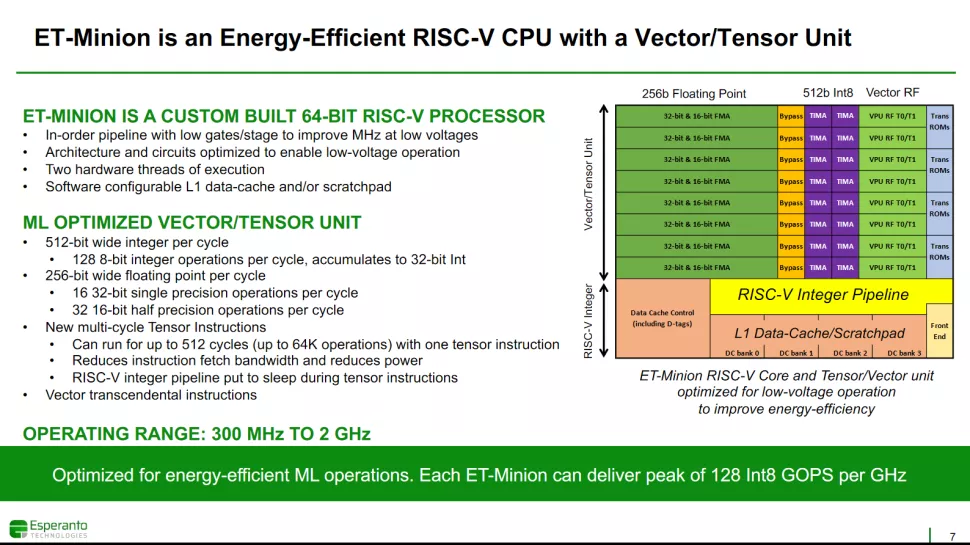

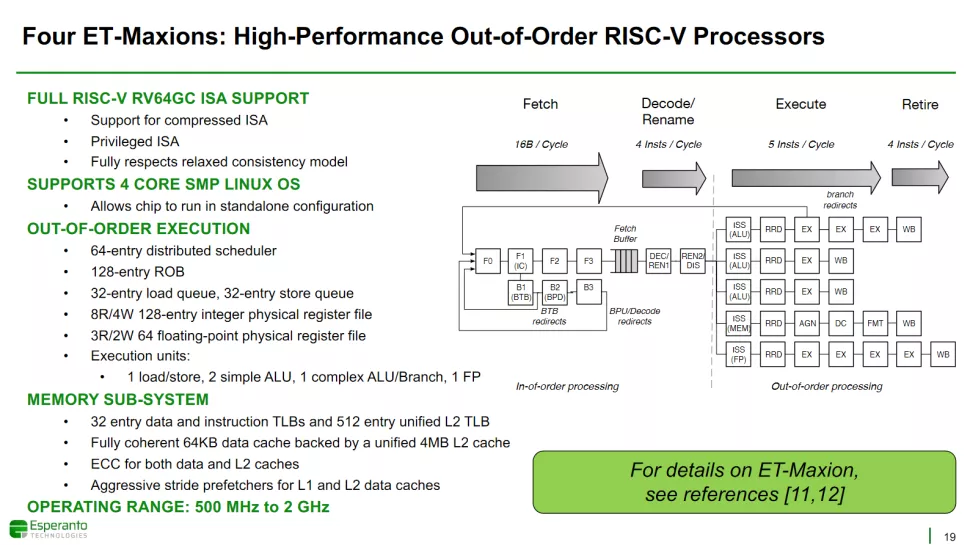

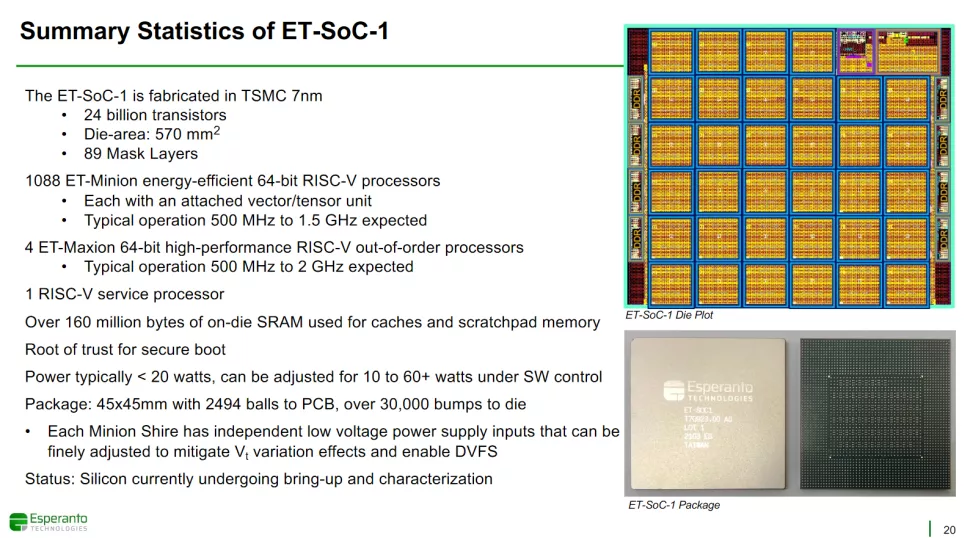

7nm工艺搭建出千核处理器

7nm工艺搭建出千核处理器

参考资料:

https://www.esperanto.ai/esperanto-technologies-unveils-energy-efficient-risc-v-based-machine-learning-accelerator-chip-at-hot-chips-33-conference/

https://nl.hardware.info/nieuws/78166/hot-chips-tsmc-stopt-20-keer-zoveel-transistoren-in-de-nieuwste-generatie-cowos

评论