傻瓜式教程:FPGA上实现MATLAB filterDesigner设计的FIR低通滤波器

0 概述

filterDesigner(在旧版本的MATLAB中被称为fdatool)是MATLAB Signal Processing Toolbox™ 中一个功能强大的图形用户界面 (GUI),用于设计和分析滤波器。本教程以FIR低通滤波器为例介绍filterDesigner的使用方法,以及如何将设计完成的滤波器在FPGA上实现。本次实验的步骤是使用双通道250 MSPS的AD采集卡对两路正弦信号进行采集,再经过混频、低通滤波后得到差频信号。

1 使用filterDesigner

设计低通滤波器

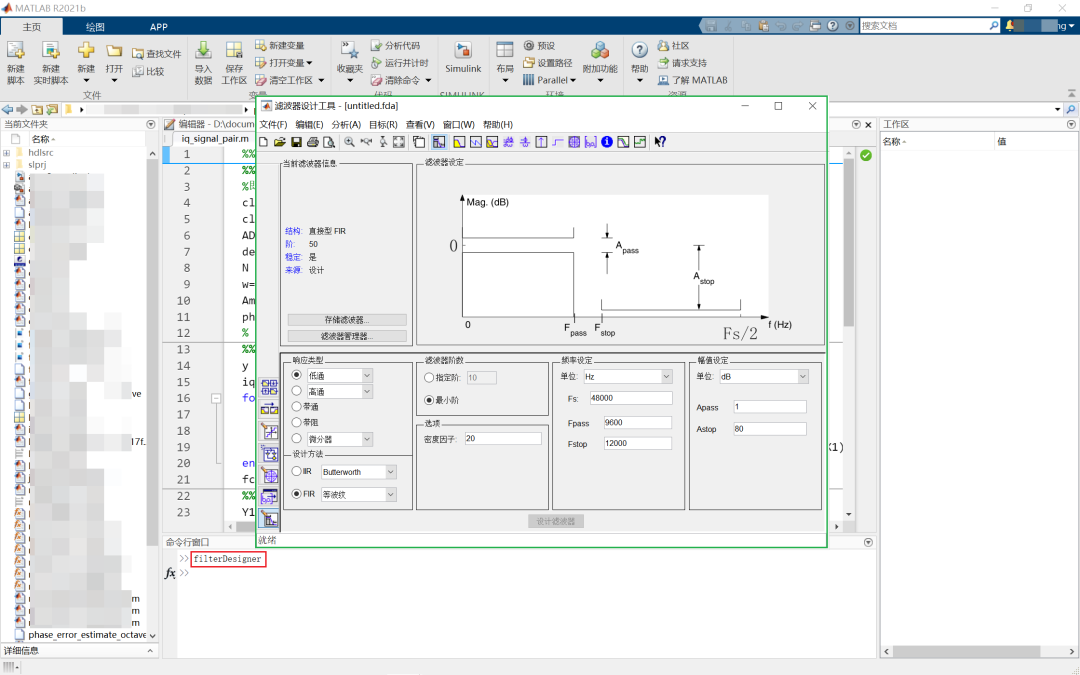

在MATLAB(本次实验所用版本为2021b)命令窗口键入“filterDesigner”打开滤波器设计工具的GUI:

图1:filterDesigner设计界面

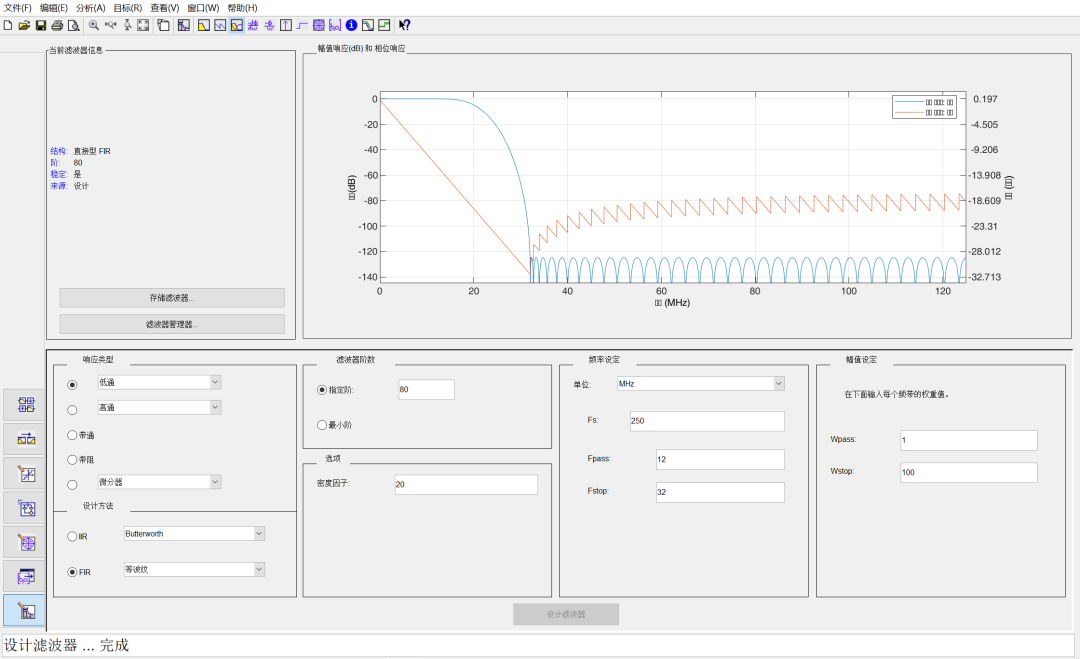

由于我们双通道采集卡的采样率为250 MSPS,假设输入信号分别为20 MHz与30 MHz的正弦信号,则和频信号为50 MHz,差频信号为10 MHz,因此我们设计的FIR低通滤波器不妨将截止频率参数如下设计:

图2:FIR低通滤波器设计参数

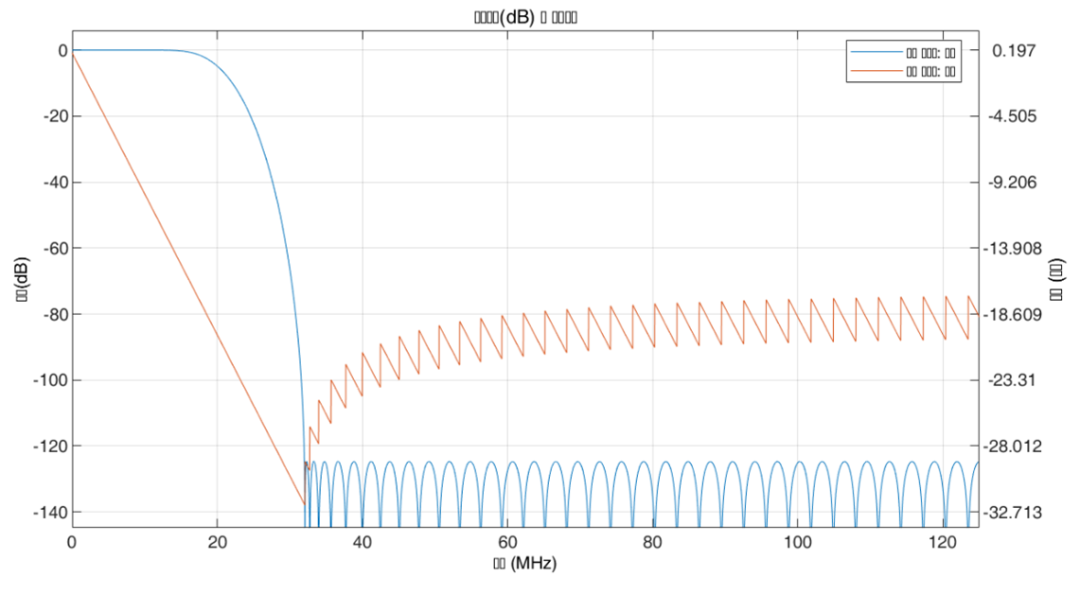

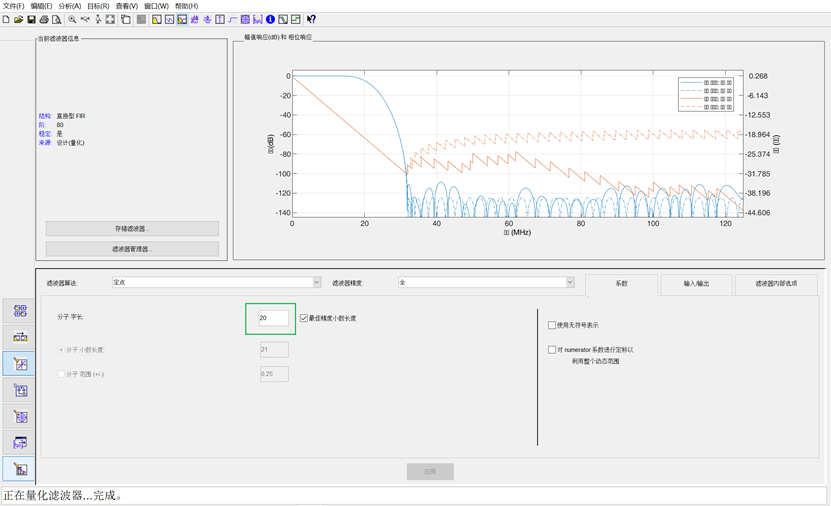

滤波器类型选择为“低通FIR等纹波(读者也可以根据项目需求选择不同的类型,例如对滤波器加窗函数等)”,采样率为250 MHz,指定阶数为80(这里只是做个滤波实验,用到的芯片为Zynq-7000系列的SoC,具体型号为XC7Z100-2FFG900,芯片的DSP48E1资源足够,所以就随便指定了,如果你做项目,一定得根据实际情况控制资源使用,否则FPGA资源可能不够你挥霍),Fpass设为12,Fstop设置为32,Wpass设为1,Wstop设为100。得到滤波器的幅频响应和相频响应如图3所示(oops,中文界面的标题乱码了):

图3:FIR低通滤波器幅频响应和相频响应

2 FIR低通滤波器量化

与系数导出

本次实验设计的FIR低通滤波器最终要在FPGA平台上运行,因此需要先将设计的滤波器参数进行量化。打开量化界面:

图4:量化界面

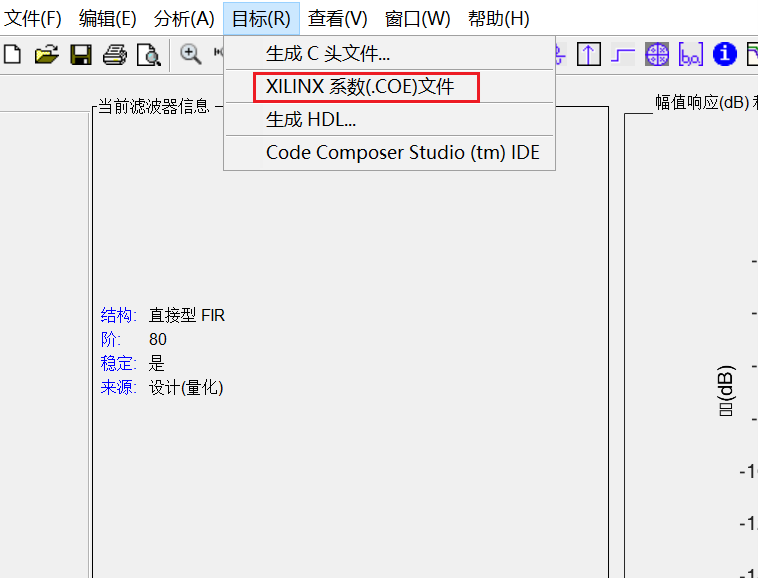

我们将字长设为20(再次提醒:要根据项目实际进行设计,此处的字长越大设计出来的数字滤波器越接近理想情况,但是相应的数据位宽也会急剧增长),可以看到低通滤波器对高频信号的衰减能够轻松达到100dB以上。其他参数设计采用默认。点击“目标”——>“XLINX系数(.COE)文件”,生成FIR_LOWPASS.coe文件(命名自定义)。

图5:.coe文件生成

本次实验得到的滤波器相关系数如下:

; XILINX CORE Generator(tm)Distributed Arithmetic FIR filter coefficient (.COE) File

; Generated by MATLAB(R) 9.11 and DSP System Toolbox 9.13.

Radix = 16;

Coefficient_Width = 20;

CoefData = 00000,

ffffb,

fffeb,

……

ffffb,

00000;

3 FIR低通滤波器

在FPGA上的实现

接下来打开FPGA开发工具VIVADO,新建工程文件(VIVADO工程创建部分不在此处详述),本次实验的流程图如下:

图6:实验流程图

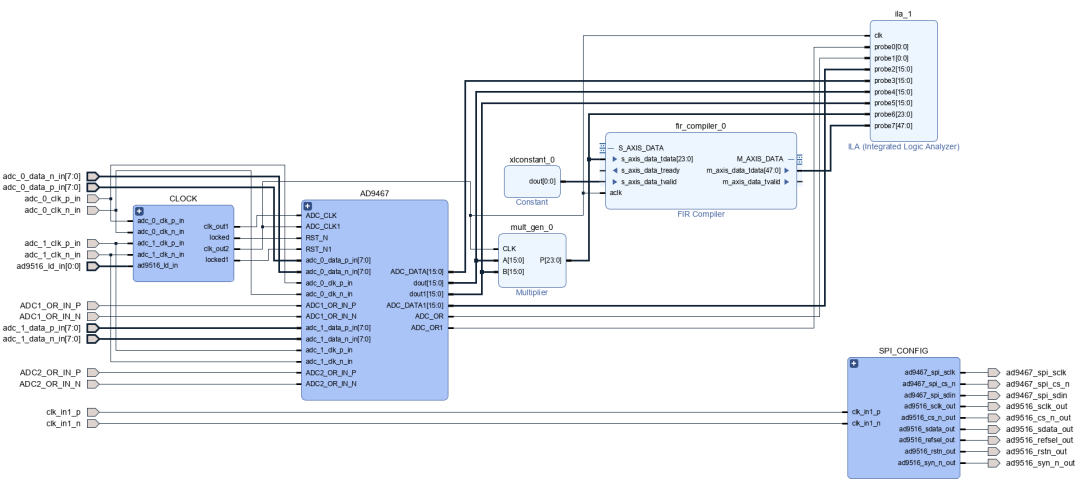

整体的block design如下:

图7:实验的整体设计

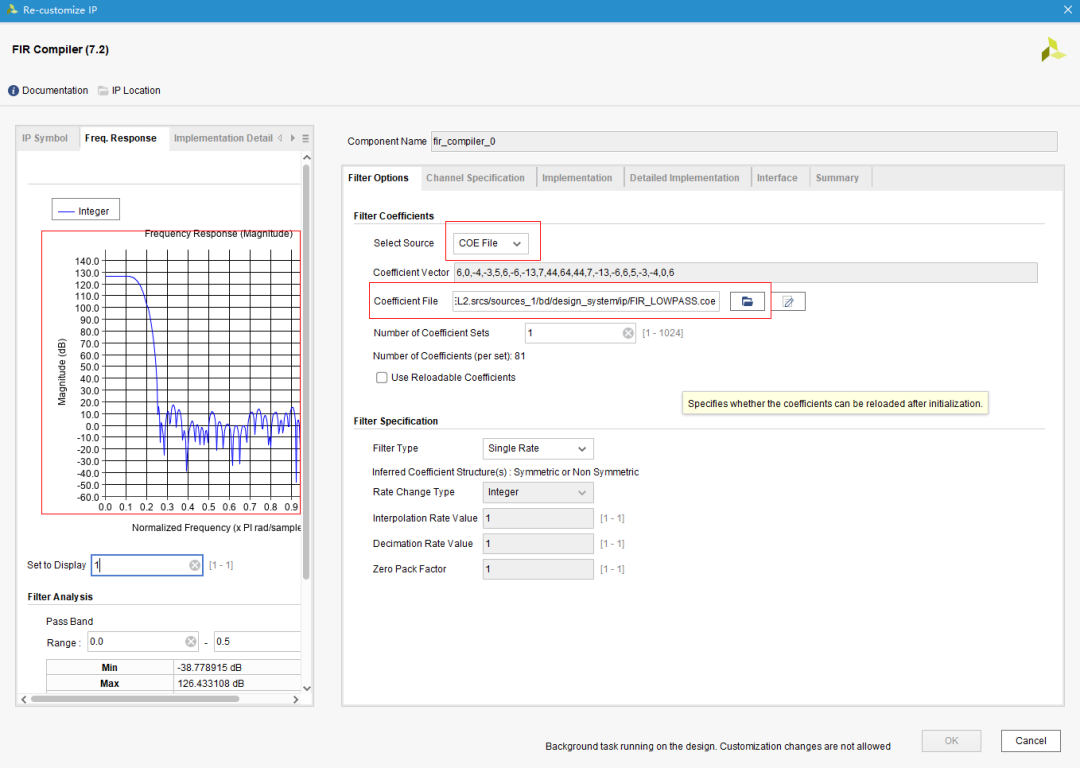

FIR的IP核配置如下,参数配置要与MATLAB设计的保持一致:

图8:导入filterDesigner设计的.coe文件

图9:IP核参数配置

4 FIR低通滤波器滤波

实验结果

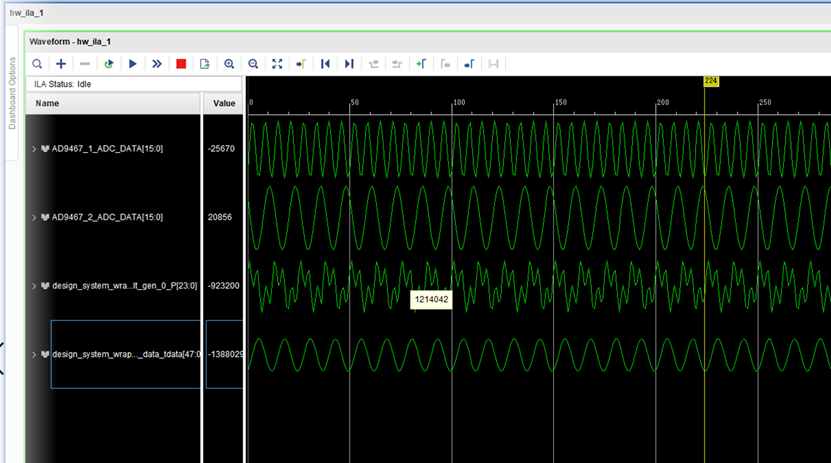

当通道1信号频率为30 MHz,通道2频率为20 MHz时,实验1滤波结果如下:

图10:实验1滤波结果

上述信号分别为:30 MHz正弦波,20 MHz正弦波,混频信号,差频10 MHz信号。

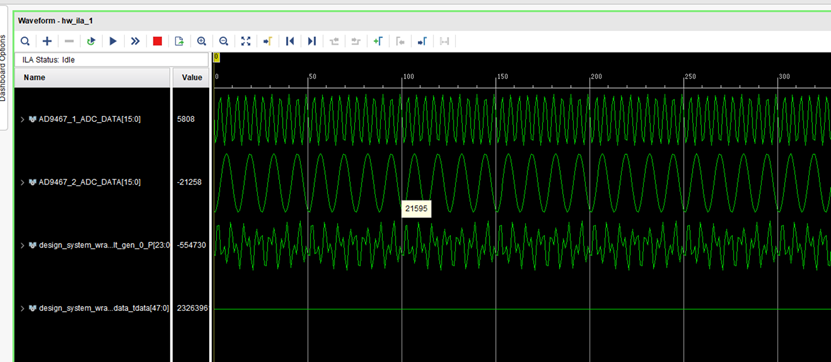

当通道1信号频率为40 MHz,通道2频率为20 MHz时,实验2滤波结果如下:

图11:实验2滤波结果

上述信号分别为:40 MHz正弦波,20 MHz正弦波,混频信号,差频20 MHz信号(可以看到信号幅值明显有衰减)。

当通道1信号频率为55 MHz,通道2频率为20 MHz时,实验3滤波结果如下:

图12:实验3滤波结果

上述信号分别为:55 MHz正弦波,20 MHz正弦波,混频信号,差频35 MHz信号(差频信号被全部衰减)。

5 结论与展望

本文介绍了使用MATLAB的filterDesigner设计FIR滤波器的流程,并介绍了如何将设计的滤波器在FPGA上实现。由于只用FPGA进行低通滤波,消耗的资源较少,读者应该根据实际项目情况设计以免资源消耗过大,无法完成项目。Xilinx的FIR滤波器除了常用的数字滤波以外,还支持动态配置以实现对资源的高效利用。读者可以根据需求对.coe系数进行重载。

长按识别二维码关注我们

微信号 :RPIBMEPhD

这是一群致力于科研传播的faculty & PhD & Postdoc记录分享点滴思考的平台,这里有我们在各自领域(机器学习,医疗影像,材料科学,凝聚态物理,生物信息,光学成像等)涉猎研究的点滴感悟,有我们在国内,海外求学工作奋斗的酸甜苦辣,亦有偶尔的风月和我们的诗与远方。

——纯真学者团队