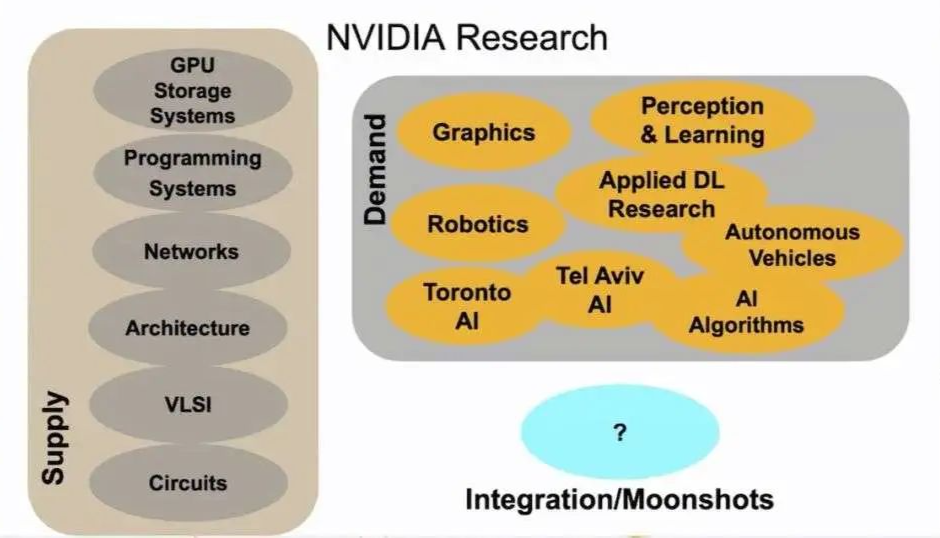

AI做显卡、显卡跑AI!英伟达实现芯片设计自循环?

点击下方卡片,关注“新机器视觉”公众号

重磅干货,第一时间送达

【导读】用AI更快更好设计显卡,再用做出的显卡跑更快更好的AI。英伟达的这个反向营销案例,非常巧妙。

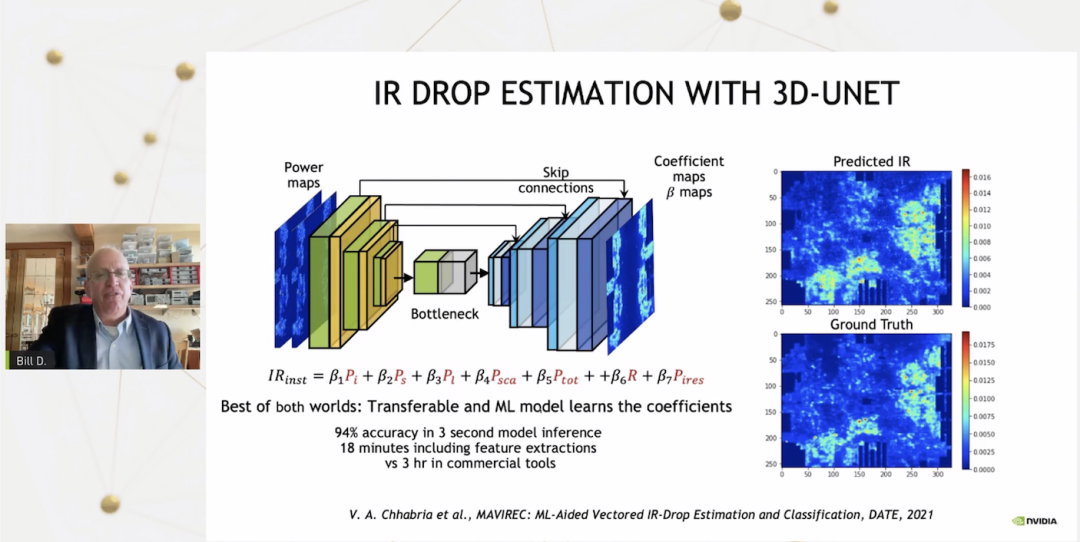

绘制电压下降图

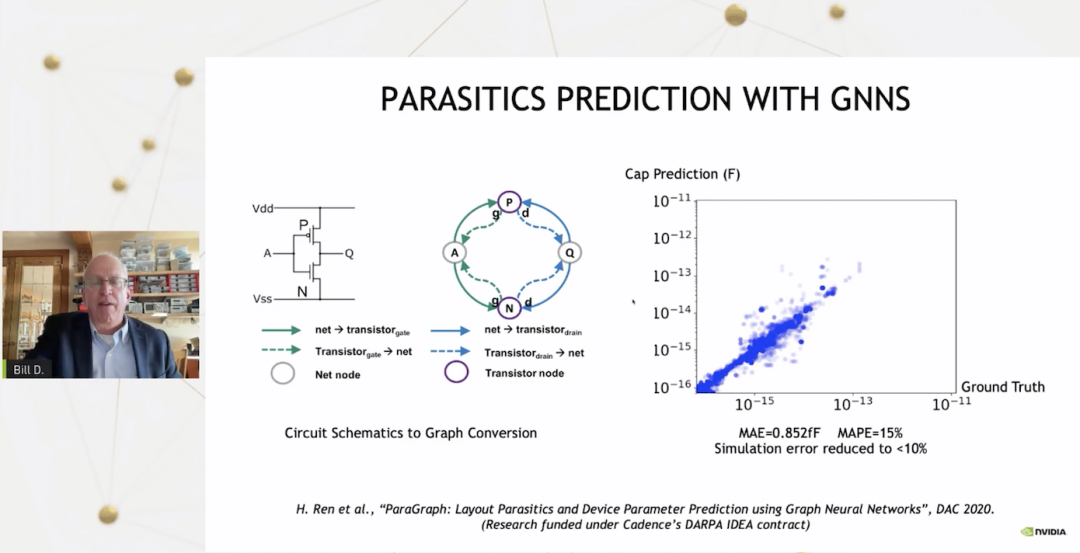

预测寄生元件

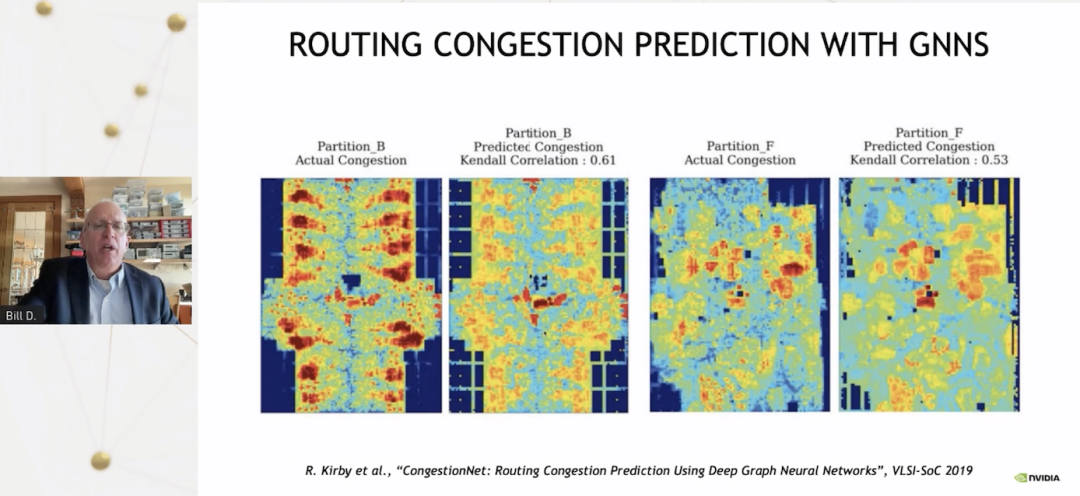

布局/布线拥塞

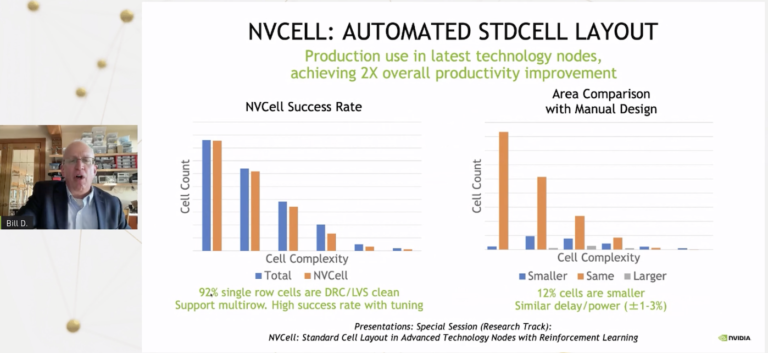

芯片标准单元设计自动化

参考资料:

https://www.hpcwire.com/2022/04/18/nvidia-rd-chief-on-how-ai-is-improving-chip-design/

本文仅做学术分享,如有侵权,请联系删文。

评论